# Enabling Power-Efficient Designs with III-V Tunnel FETs

Moon Seok Kim, Huichu Liu, Karthik Swaminathan, Xueqing Li, Suman Datta, Vijaykrishnan Narayanan

The Pennsylvania State University, University Park, PA, 16802, US Email: {mqk521, hxl249, kvs120, lixueq}@cse.psu.edu; sdatta@engr.psu.edu, vijay@cse.psu.edu

Abstract — III-V Tunnel FETs (TFET) possess unique characteristics such as steep slope switching, high  $g_{\rm m}/I_{\rm DS}$ , unidirectional conduction, and low voltage operating capability. These characteristics have the potential to result in energy savings in both digital and analog applications. In this paper, we provide an overview of the power efficient properties of III-V TFETs and designs at the device, circuit and architectural level.

Index Terms — Steep-slope devices, ultra-low power, low-voltage, III-V Tunnel FET (TFET).

### I. INTRODUCTION

As technology continues to scale down to the nanometer regime, circuit designers and architects are forced to grapple with problems related to power constraints at various levels of abstraction. The limitation in available power results in a variety of design implications, ranging from reduced battery life in low end mobile processors to increased cooling costs in high performance systems and data centers. Consequently, efforts are being made to realize new power-efficient designs. At the device level, this focuses on new efforts to lower supply voltage by exploring new device architectures and material systems.

Supply voltage scaling in silicon based CMOS transistors has been a significant challenge due to the conflict between the scaling down of threshold voltage for performance and the increased leakage. Enhancements to device architecture such as improved electrostatics using multi-gate devices help to lower supply voltage while retaining the threshold voltage constant. Similarly, III-V materials offer the ability to improve the electron mobility at the same field strength. Recent technology nodes have seen concurrent enhancements in both the device and material systems. However, the switching slope of the CMOS transistors is fundamentally limited to the 60mV/decade swing. This paper focuses on III-V Steep slope Tunnel Field-Effect Transistors (TFETs) that aim at overcoming this limit.

TFET [1, 2] has emerged as a strong candidate for lowenergy applications due to its superior energy efficiency arising from the sub-thermal (Sub-kT) switching characteristics at low supply voltages. In addition to the steep switching characteristics, a combination of unique features of TFETs such as asymmetrical source/drain design, and uni-directional conduction provide new opportunities and challenges for analog and digital design.

This paper highlights on how advances in GaSb-InAs (III-V) HTFET design influence circuit and architectural level implementations of digital and analog systems. The rest of the paper is organized as follows: Section II describes the TFET device design and introduces recent progress and modeling efforts. Section III discusses TFET architecture and digital designs for energy efficient systems. Section IV focus on the TFET advantages for analog systems. Conclusions are followed in Section V.

### II. OVERVIEW OF THE TUNNEL FET DEVICES

### A. Tunnel FET Device Design

TFETs have become one of the most promising candidates to enable the voltage scaling [1]. Unlike MOSFETs, a TFET is essentially a gated p-i-n tunnel diode with asymmetrical source/drain doping [2]. Benefitting from the band-to-band tunneling (BTBT) induced carrier injection at the source-channel junction, the high energy carriers with an energy slope of kT (where k is the Boltzman constant, T is the absolute temperature) are filtered by a tunneling window, leading to a subthermal energy switching slope in TFETs.

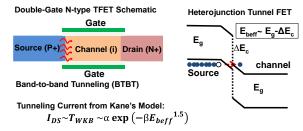

Fig. 1. TFET schematic and band diagram of a hetero-junction TFET for effective tunnel barrier (E  $_{\!\!\!\text{beff}})$  reduction.

Recent progress in prototype device and circuit demonstration has shown prominent advantages of TFETs for various energy efficient applications. To outperform CMOS at low supply voltages, the device characteristics such as high on-current at low voltage, high on/off ratio

and steep sub-threshold swing at room temperature are the key performance aspects of a TFET. Hence, choices of material system and device architecture are critical in TFET design, such as using the hetero-band alignment and low bandgap material to improve the tunneling current, improving the gate electrostatic control from planar to nanowire or ultra-thin body, and reducing defect states to suppress the trap-assisted tunneling [3] (Fig. 1). Knoll et al [4] demonstrated the first strained Si nanowire inverter showing sharp transition at 0.2 V. Considering the low tunneling current of Si TFETs, III-V semiconductor materials offer more freedom of engineering the tunnel junctions and improving the tunneling current [5]. Dewey et al in [6] first explored InGaAs homojunction and heterojunction TFET (HTFET) with improved on-current than Si TFET. Mohata et al [7] demonstrated a MOSFETlike on-current in  $GaAs_{0.35}Sb_{0.65}/In_{0.7}Ga_{0.3}As$  heterojunction TFET, by taking advantage of the effective tunneling barrier reduction at the source-channel junction without reducing the band-gap of the channel material, which led to a simultaneous enhancement of the I<sub>ON</sub> and I<sub>ON</sub>/I<sub>OFF</sub> ratio. Later on, a further improvement of oncurrent of 180 µA/µm has been achieved by Zhou et al [8] in a GaSb-InAs TFET. Recent advancement in complementary TFET process [9, 10] has further highlighted both the performance improvement and process compatibility for TFET technology.

### B. Tunnel FET Modeling for Circuit Simulation

To enable the TFET-based circuit designs and system analysis, compact model development is critical for emerging devices. Several works [11, 12] have explored analytical modeling for different designs of TFETs. Zhang et al [11] have developed a compact model of double-gate Si TFET for SPICE simulations, showing good agreement with TCAD simulation. Recently, Lu et al [12] present a continuous semi-empirical model to accurate describe the current-voltage characteristics suitable for both InAs homojunction TFETs and broken-gap AlGaSb/InAs TFETs. Given the variety of TFET designs and lack of mature SPICE models for III-V TFETs, look-up based Verilog-A models derived from atomistic simulation [13] or TCAD [14] have been widely used to explore circuit/architectural designs.

Process variation and electrical noise pose a growing reliability concern for optimal system design for both digital and analog/RF applications at scaled technology nodes, especially due to the preferred low supply voltage operation of TFETs. The process variation for III-V HTFETs have been studied for TFET SRAMs [14] and logics [13]. When variations are considered, the energy savings of III-V HTFET logic gates are slightly reduced,

but still superior compared to CMOS [27]. Moreover, the electrical noise performance has been evaluated in [15] for III-V HTFETs including the flicker, shot and thermal noise. At a nominal operation voltage of 0.3 V, HTFET exhibits a competitive input-referred noise in KHz and MHz frequency range compared to the baseline Si FinFET. When the operating voltage exceeds 0.3 V for a frequency range of 10GHz or higher (RF domain), the HTFET input-referred noise increases moderately due to the presence of shot noise.

The progress in TFET modeling for circuit simulation has enabled the circuit-level and architecture-level explorations of the energy efficiency benefits of TFETs, such as TFET digital and analog circuits [16-19], TFET-CMOS heterogonous architecture [20] as well as the TFET standard cell library development [21].

### III. TUNNEL FET CIRCUITS EXPLORATION

By taking advantage of the unique III-V hetero-junction TFET device characteristics, it is promising to design analog and digital circuits with novel functions and/or superior performance. In the rest of this section, a review of recent reported TFET circuits and applications is provided in comparison with Si FinFET designs.

# A. Tunnel FET Digital Logic Design Opportunities

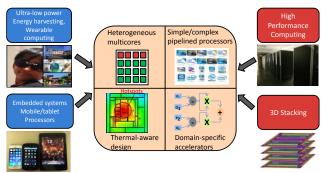

These characteristics of HTFETs can manifest themselves in various system-level design techniques that make this technology attractive across a wide range of application domains. Fig. 2 shows the potential scope of applications domains that would benefit from the adoption of HTFET technology into their design. For instance, heterogeneous CMOS-TFET multicores could be used to optimize a wide range of sequential and parallel workloads. The efficiency of TFET at low voltage makes it highly energy-efficient in executing highly parallel workloads using tens of low-voltage cores operating at low frequencies. Similarly, it is possible to duplicate the performance of a high frequency CMOS processor with TFET processors of higher micro-architectural complexity by consuming much less power, by simply lowering the operating voltage and frequency. In a similar manner, the lower power density of TFET processors can translate into more effective elimination of temperature hotspots, making them feasible candidates for thermal-aware systems. This aspect would also be useful in state-of-theart techniques like 3D stacking of processors and memory, where thermal effects are a significant concern. Finally, HTFET designs can also be extremely useful in realizing power-efficient, domain-specific accelerators [20].

Fig. 2. Design Spaces for Device Heterogeneous Systems.

Designing the HTFET processors used in the domains stated above require efficiently re-designing the constituent digital circuit components present in these processors. Energy-efficient adders, inverters and other combinational logic have been demonstrated in prior efforts [22]. For example, for the energy-delay performance of 32-bit adders, the energy consumed by the HTFET adder is one order less than that of a Si FinFET adder for the requirement of 1 nS delay.

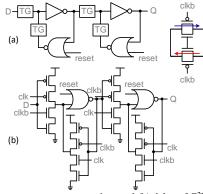

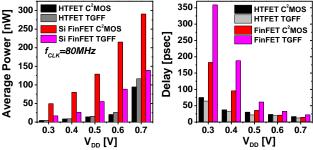

Fig. 3. (a) Average power consumption, and (b) delay of C<sup>2</sup>MOS and TG flip-flops at 0.3-0.7 V.

Fig. 4. (a) Average power consumption, and (b) delay of C<sup>2</sup>MOS and double TGs (transmission gates) flip-flops at 0.3-0.7 V.

Flip-flop is a key component in digital circuits. In [17], the energy efficiency and performance of TFET flip-flop designs are discussed, where HTFET flip-flops reduces 2.5 times power consumption compared with the Si FinFET designs. Fig. 4 shows the average power consumption and

delay performance for two types of the popular master/slave flip-flop topologies with an additional port (reset) at various supply voltage ranges. From the simulation results, HTFET flip-flops shows the high power-efficiency and fast transition performance at a power supply lower than 0.5 V due to steep slope switching.

### B. Tunnel FET Analog Circuits Design Opportunities

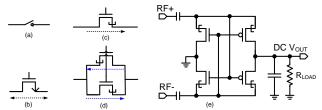

One unique feature of TFET is the uni-directional conduction ability, which turns out to be useful in applications like charge pumps where the TFET are working as switches. Fig. 5 shows a widely-used conventional switch design using one single MOSFET. When the switch is turned on, current could flow from either terminal of the switch to the other, with the current direction depending on the terminal voltage. When the MOSFET in Fig. 5 is replaced by a TFET, this bidirectional current conduction phenomenon is changed to be uni-directional.

Fig. 5. (a) Ideal On/Off switch; (b) NMOS switch with bidirectional current conduction; (c-d) Uni-directional/bidirectional N-type/2N-type TFET switches; (e) RF rectifier using TFETs.

Fig. 5(e) shows a conventional rectifier topology in which transistors behave as switches [18]. One major power loss that limits the power conversion efficiency (PCE) in CMOS rectifiers is the reverse leakage current. Such leakage current transports the charge at the output towards the input, resulting in significant undesirable output voltage drop and efficiency degradation. In contrast, the reverse leakage could be simply prevented using TFET devices without modifications to the circuit topology. Therefore, the PCE could be improved. Similarly, for conventional DC-DC charge pumps, such bidirectional conduction could also result in reverse leakage current. [23]. In contrast, utilizing TFET in such designs could reduce the reverse leakage current and improve the PCE.

Another feature that contributes to a higher PCE is the steep-slope switching at low input voltage that helps to reduce the turn-on resistance and accordingly, reduce the power loss. As a result, compared with the Si FinFET, the TFET enables both AC-DC conversion and DC-DC conversion under a low input voltage with a higher PCE.

High g<sub>m</sub>/I<sub>DS</sub> helps to achieve high power efficiency in analog designs. In [19], the authors presented a TFET neural amplifier design employing a telescopic operational

trans-conductance amplifier (OTA) for multi-channel biosignal recording. For such amplifier design, low power to prevent burning the body tissue, high gain and low inputreferred noise to sense weak signals are key design specifications. By exploring the high  $g_m/I_{DS}$  advantage of TFETs, the neural amplifier exhibited high current efficiency, high voltage gain, and also low input-referred noise. A noise efficiency factor was reduced significantly compared to the theoretical limit of CMOS amplifiers.

With the transistor process scaling and the system application developing, the analog circuits design is becoming challenging [24]. On the one hand, the requirements are more stringent with higher resolution, faster speeds, lower power, and larger dynamic range. On the other hand, the transistors are getting less dependable in terms of matching, voltage range, leakage and reliabilities even if getting faster. Under circumstances, more and more digital assisted/enhanced techniques are being proposed to compensate these nonidealities, and analog circuits design are becoming more and more "digital". For example, digital calibration is widely used in analog-to-digital converters (ADC) to improve the effective number of bits (ENOB) and signalto-noise-and-distortion ratio (SNDR) [25]; Pre-distortion could be applied to improve the linearity of power amplifier (PA) and digital-to-analog converters (DAC) [25]; Phase-locked loops (PLL) could even be built nearly digitally [26]. Considering the fact that the advantage of using TFET to build these digital assisting blocks remains, TFETs will be showing more advantages in designing future analog and mixed-signal circuits.

### VII. CONCLUSION

In this paper, new opportunities of using the III-V hetero-junction Tunnel FETs have been reviewed from device, circuits, and system-level perspectives. Progress in III-V Tunnel FET devices can have a significant impact on the landscape of energy-efficient systems.

## ACKNOWLEDGMENT

This work was supported by the LEAST, one of the six SRC STARnet Centers, sponsored by MARCO and DARPA. The NSF award 1205618 supported equipment used in this effort. This work is also supported in part by NSF ASSIST Nanosystems ERC EEC-1160483.

### REFERENCES

[1] Nikonov, D. E., et al, "Uniform methodology for benchmarking beyond-CMOS logic devices," in IEEE IEDM Tech. Dig., p.25.4.1-25.4.4, 2012.

- [2] A. Seabaugh et al, "Low-Voltage Tunnel Transistors for Beyond CMOS Logic", IEEE Proc., vol. 98, iss. 12, pp. 2095-2110, 2010.

- [3] J. Knoch et al, "A novel concept for field-effect transistors the tunneling carbon nanotube FET," in DRC '05, p.153-156, 2005.

- [4] L. Knoll et al, "Demonstration of improved transient response of inverters with steep slope strained Si NW TFETs by reduction of TAT with pulsed I-V and NW scaling," in IEDM, pp.4.4.1-4.4.4, 2013

- [5] S. Datta, et al., "Tunnel Transistors for Energy Efficent Computing" in *IEEE Int. Rel. Physics Symp. (IRPS)*, 2013.

- [6] G. Dewey et al, "Fabrication, characterization, and physics of III-V heterojunction tunneling field effect transistors (HTFET) for steep sub-threshold swing," in IEDM, p.33.6.1-33.6.4, Dec. 2011.

[7] D. K. Mohata et al. "Demonstration of improved heteroepitaxy,

- [7] D. K. Mohata et al. "Demonstration of improved heteroepitaxy, scaled gate stack and reduced interface states enabling heterojunction Tunnel FETs with high drive current and high onoff ratio" in VLSIT, pp. 53–54, Jun 2012.

- [8] G. Zhou et al, "Novel gate-recessed vertical InAs/GaSb TFETs with record high  $I_{ON}$  of  $180\mu A/\mu m$  at  $V_{DS}{=}0.5V$ ," in IEDM, p.32.6.1-32.6.4, 2012.

- [9] K. Tomioka et al, "Integration of III-V nanowires on Si: From highperformance vertical FET to steep-slope switch," in IEDM, pp.4.1.1,4.1.4, 2013.

- [10] R. Rooyackers et al, "A new complementary hetero-junction vertical Tunnel-FET integration scheme," in IEDM, pp.4.2.1-4.2.4, 2013.

- [11] L. Zhang et al, "SPICE modeling of double-gate tunnel-FETs including channel transports," *TED*, vol.61, no.2, p.300,307, 2014.

- [12] H. Lu et al, "Continuous Semiempirical Model for the Current Voltage Characteristics of Tunnel FETs", in ULIS, 2014.

- [13] U. E. Avci et al, "Energy efficiency comparison of nanowire heterojunction TFET and Si MOSFET at L<sub>g</sub>=13nm, including P-TFET and variation considerations," in *in IEEE IEDM Tech. Dig.*, pp.33.4.1, 33.4.4, Dec. 2013.

- [14] V. Saripalli et al., "Variation-tolerant ultra low-power heterojunction tunnel FET SRAM design," *IEEE/ACM Int. Symp. on Nanoscale Arch. (NANOARCH)*, vol. 1, pp. 45–52, Jun. 2011.

- [15] R. Pandey et al, "Electrical Noise in Heterojunction Interband Tunnel FETs," *TED*, vol.61, no.2, pp.552,560, Feb. 2014.

- [16] I. Palit et al, "TFET-based cellular neural network architectures," in *ISLPED*, pp.236,241, Sept. 2013.

- [17] M. Cotter et al, "Evaluation of tunnel FET-based flip-flop designs for low power, high performance applications," in *ISQED*, pp.430,437, 2013.

- [18] H. Liu, et al, "TFET-based ultra-low power, high-sensitivity UHF RFID rectifier," in *ISLPED*, pp.157-162, 2013.

[19] H. Liu et al, "Tunnel FET-Based Ultra-Low Power, Low-Noise

- [19] H. Liu et al, "Tunnel FET-Based Ultra-Low Power, Low-Noise Amplifier Design for Bio-signal Acquisition", in *ISLPED*, 2014 (accepted).

- [20] K. Swaminathan et al, "An Examination of the Architecture and System-level Tradeoffs of Employing Steep Slope Devices in 3D CMPs", in *ISCA'14*, June, 2014 (accepted).

- [21] K. Swaminathan et al, "Modeling steep slope devices: From circuits to architectures," in *DATE*, pp.1,6, 24-28 2014

- [22] R. Mukundrajan, et al, "Ultra Low Power Circuit Design using Tunnel FETs" in ISVLSI2012, 2012.

- [23] Dongsheng Ma, Rajdeep Bondade, "Reconfigurable Switched Capacitor Power Converters," *Springer*, 2013.

- [24] Anne-Johan Annema et al, "Analog circuits in ultra-deep-submicron CMOS," JSSC, vol. 40, pp. 132-143, Jan. 2005.

- [25] Murmann, B., "Digitally assisted data converter design," in 2013 Proc. of ESSCIRC, pp.24, 31, 2013.

- [26] Staszewski et al, "All-digital PLL and transmitter for mobile phones," JSSC, vol.40, no.12, pp.2469,2482, Dec. 2005.

- [27] K. Swaminathan et al, "Steep Slope Devices: Enabling New Architectural Paradigms," in DAC, 2014 (accepted).