# Structural, morphological, and defect properties of metamorphic In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> p-type tunnel field effect transistor structure grown by molecular beam epitaxy

Yan Zhu and Mantu K. Hudaita)

Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, Virginia 24061

Dheeraj K. Mohata, Bijesh Rajamohanan, and Suman Datta

Electrical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802

Dmitri Lubyshev, Joel M. Fastenau, and Amy K. Liu *IQE Inc.*, *Bethlehem*, *Pennsylvania* 18015

(Received 12 April 2013; accepted 17 June 2013; published 3 July 2013)

Structural properties of metamorphic  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  p-type tunnel field effect transistor (TFET) structure grown by molecular beam epitaxy were comprehensively investigated. High resolution x-ray diffraction revealed symmetric strain relaxation and pseudomorphic  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  active layers with respect to the  $In_{0.7}Al_{0.3}As$  buffer, indicating a low dislocation density within the active region. The surface morphology of this structure exhibited a typical two-dimensional cross-hatch pattern with a low root-mean-square roughness of 2.58 nm. Cross-sectional transmission electron microscopy demonstrated a low threading dislocation density within the active region, suggesting high crystalline quality of this p-type TFET structure. Dynamic secondary ion mass spectrometry exhibited an abrupt doping profile over the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  source/channel junction as well as minimal level of intermixing between As and Sb atoms. Thus, these structural properties showed high quality of this structure and provided critical guidance for the fabrication of As/Sb based staggered gap complementary TFETs for ultra-low standby power and energy efficient logic applications. © 2013 American Vacuum Society. [http://dx.doi.org/10.1116/1.4812793]

## I. INTRODUCTION

Power dissipation is a critical bottleneck for further scaling of metal-oxide-semiconductor field-effect-transistors (MOSFETs) to nanoscale. Reducing the supply voltage of transistors is one of the most promising approaches to lower power dissipation while preserving high device performances.<sup>1</sup> However, the limitation of MOSFETs to a minimum subthreshold slope (SS) of 60 mV/dec at room temperature (RT) becomes a major obstacle to further reduce the supply voltage while maintaining high ON/OFF-ratio.<sup>1,2</sup> Tunnel fieldeffect-transistors (TFETs)<sup>1-11</sup> would exhibit steep (<60 mV/ dec at RT) subthreshold characteristics due to the tunneling injection of carriers from source to channel, rather than by thermionic emission. Recently, with the demonstration of sub-60 mV/dec SS (Ref. 3) and MOSFET-like ON-current at RT, 4,5 III-V TFETs have attracted significant interest as low supply voltage transistors for future low power logic applications. 6-11 Among all III-V materials, 3-16 type-II staggered gap In<sub>x</sub>Ga<sub>1-x</sub>As/GaAs<sub>v</sub>Sb<sub>1-v</sub> heterostructures have been demonstrated to simplify the design approach and tailor the device performance for applications over a wide range via material composition modulation. 4-16 In recent years, great efforts have been devoted to investigate and upgrade the structural properties and device performances of n-type In<sub>x</sub>Ga<sub>1-x</sub>As/GaAs<sub>y</sub>Sb<sub>1-y</sub> staggered gap TFETs.<sup>4-14</sup> It is equally important to study high-quality p-type TFET structures within the same material system to achieve complementary energy efficient logic circuits. <sup>16,17</sup> In this work, a comprehensive study was carried out on the structural properties of a metamorphic In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> p-type staggered gap TFET structure grown by molecular beam epitaxy (MBE). The experimental results demonstrated high material quality of this TFET structure.

## II. EXPERIMENT

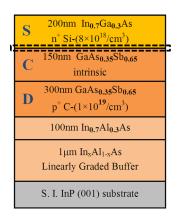

The In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> p-type staggered gap TFET structure was grown by solid source MBE on semiinsulating (100) InP substrate and the schematic layer structure is shown in Fig. 1. The source (S), channel (C) and drain (D) regions are labeled in this figure and the In<sub>0.7</sub>Ga<sub>0.3</sub>As/ GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface is denoted in a box. As shown in Fig. 1, there is 1.2% lattice mismatch between active layers (In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub>) and the InP substrate. To accommodate this lattice mismatch,  $1\mu$ m linearly graded In<sub>x</sub>Al<sub>1-x</sub>As buffer layer was grown with indium (In) composition increasing from 52% to 70% and aluminum (Al) composition decreasing from 48% to 30% so that the top of the buffer layer (100 nm In<sub>0.7</sub>Al<sub>0.3</sub>As) is internally lattice matched to the GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel/drain layers. The active region of this p-type TFET structure consists of 200 nm n<sup>+</sup> In<sub>0.7</sub>Ga<sub>0.3</sub>As source layer with silicon (Si) doping of  $8 \times 10^{18}$ /cm<sup>3</sup>, 150 nm intrinsic GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel layer and 300 nm p<sup>+</sup> GaAs<sub>0.35</sub>Sb<sub>0.65</sub> drain layer with carbon (C) doping of  $1 \times 10^{19}$ /cm<sup>3</sup>. The linearly graded  $In_xAl_{1-x}As$ buffer, the GaAs<sub>0,35</sub>Sb<sub>0,65</sub> channel and drain layers and the

a)Electronic mail: mantu.hudait@vt.edu

Fig. 1. (Color online) Schematic diagram of the metamorphic  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  p-type TFET layer structure. The source (S), channel (C), and drain (D) regions are labeled in this figure and the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterointerface is denoted in a box.

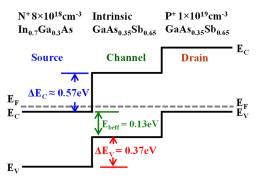

In<sub>0.7</sub>Ga<sub>0.3</sub>As source layer were grown with an optical pyrometer temperature of 500 °C. The active region of this p-type TFET structure was grown with a uniform growth rate of 2.5 Å/s. The n<sup>+</sup> In<sub>0.7</sub>Ga<sub>0.3</sub>As source and the gated intrinsic GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel formed the tunnel junction, which is essential for the operation of p-type TFET. Engineering an abrupt In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface is critical for the staggered gap TFET structure. However, the abrupt switching from mixed-anion GaAs<sub>0.35</sub>Sb<sub>0.65</sub> to mixed-cation In<sub>0.7</sub>Ga<sub>0.3</sub>As is a significant growth challenge due to different surface sticking coefficients of arsenic (As) and antimony (Sb) at the specific growth temperature. 13 Earlier studies<sup>12,13</sup> have demonstrated that two surface terminations, i.e., (a) GaAs-like and (b) InAs-like can be formed from Sb rich GaAs<sub>0.35</sub>Sb<sub>0.65</sub> to As rich In<sub>0.7</sub>Ga<sub>0.3</sub>As. Besides, the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> TFET structure with InAs-like heterointerface shows much more superior material quality and device performances compared with the GaAs-like interface structure in an n-type TFET.<sup>12</sup> As a result, the same switching sequence and interface engineering method<sup>12</sup> as the n-type TFET structure with InAs-like interface was used during the growth of this p-type TFET structure to achieve an InAs-like heterointerface at In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> junction. The staggered source/channel band alignment with a valence band offset ( $\Delta E_V$ ) value of 0.37 eV of this structure was confirmed by x-ray photoelectron spectroscopy. 16 The schematic band alignment of the p-type In<sub>0.7</sub>Ga<sub>0.3</sub>As/ GaAs<sub>0.35</sub>Sb<sub>0.65</sub> TFET structure is shown in Fig. 2. The measured valence band offset, calculated conduction band offset and effective tunneling barrier height (E<sub>beff</sub>) were also labeled in this figure.

The strain relaxation and defect properties of the p-type TFET structure were characterized by high-resolution x-ray diffraction (XRD) and cross-sectional transmission electron microscopy (TEM), respectively. Both XRD rocking curve ( $\omega/2\theta$  scan) and reciprocal space maps (RSMs) were obtained using Panalytical X'pert Pro system with Cu K $\alpha$ -1 as x-ray source. TEM samples were prepared using conventional mechanical thinning procedure followed by Ar<sup>+</sup> ion milling. Contact mode atomic force microscopy (AFM) was

Fig. 2. (Color online) Schematic band diagram of the metamorphic  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  p-type TFET structure. The measured valence band offset, calculated conduction band offset, and effective tunneling barrier height ( $E_{beff}$ ) were also labeled in this figure.

used to characterize the surface morphology of the TFET structure. Dynamic secondary ion mass spectrometry (SIMS) using Cameca IMS-7f GEO with Cs<sup>+</sup> as primary ion beam was used to determine the compositional profiles, doping concentration and the atomic intermixing.

## III. RESULTS AND DISCUSSION

#### A. Strain relaxation properties

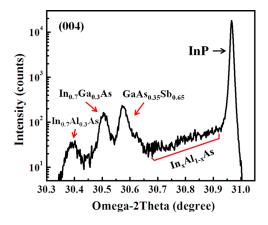

The symmetric (004) XRD rocking curve of this p-channel TFET structure is shown in Fig. 3. Each layer was labeled to its corresponding peak based on wet chemical etching experiments. According to the epilayer structure as shown in Fig. 1, the In<sub>0.7</sub>Al<sub>0.3</sub>As buffer layer, the GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel/drain layer and the In<sub>0.7</sub>Ga<sub>0.3</sub>As source layer were designed to be internally lattice matched. However, due to the residual strain within the In<sub>0.7</sub>Al<sub>0.3</sub>As buffer layer, sa well as heavily carbon (C) doping induced lattice contraction as where separate peaks in the XRD rocking curve spectrum as shown in Fig. 3. The distinct XRD peak positions suggest different lattice constants within each epilayer, which indicates different strain relaxation states of the epilayers. The detailed strain relaxation states and residual

Fig. 3. (Color online) Symmetric (004) x-ray rocking curve of the metamorphic  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  p-type TFET structure. Each layer was labeled to its corresponding peak based on early performed wet chemical etching experiments.

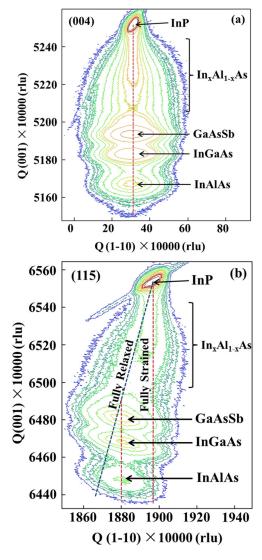

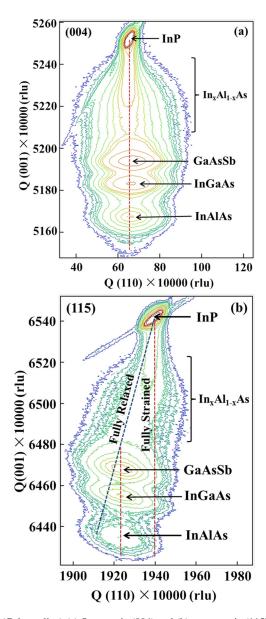

Fig. 4. (Color online) (a) Symmetric (004) and (b) asymmetric (115) RSMs of the p-type TFET structure with the incident x-ray beam along  $[1\bar{1}0]$  direction. The RSMs together with the extracted lattice parameters confirmed the pseudomorphic nature of the active layers ( $In_{0.7}Ga_{0.3}As$  and  $GaAs_{0.35}Sb_{0.65}$ ) respect to the  $In_{0.7}Al_{0.3}As$  buffer, which indicates that low dislocation density should be expected within the active layers.

strain of each epilayer were analyzed from symmetric (004) and asymmetric (115) RSMs. Figures 4(a) and 4(b) show the symmetric (004) and asymmetric (115) RSMs of the p-type TFET structure with incident x-ray beam along [110] direction. Four distinct reciprocal lattice points (RLPs) were

found in RSMs of this structure, corresponding to (1) the InP substrate, (2) GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel/drain layer, (3)  $In_{0.7}Ga_{0.3}As$  source layer and (4) 100 nm  $In_{0.7}Al_{0.3}As$ , the uppermost layer of the linearly graded In<sub>x</sub>Al<sub>1-x</sub>As buffer. From RSMs, the lattice constant in the out-of-plane, c (from the symmetric 004 reflection), and the lattice constant in the growth plane, a (from the asymmetric 115 reflection), were determined. The relaxed lattice constant  $a_r$  and strain relaxation values were also extracted from RSMs. Table I summarized the in-plane and out-of-plane lattice constants, relaxed lattice constants, strain relaxation values, residual strain and alloy composition of each epilayer with the projection of xray beam along [110] direction. Using the extracted lattice constant values in Table I, it can be seen that the active layers (In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0.35</sub>Sb<sub>0.65</sub>) are pseudomorphic to the In<sub>0.7</sub>Al<sub>0.3</sub>As buffer, which indicates that low dislocation density should be expected within the active layers. Besides, the low dislocation density within the In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0.35</sub>Sb<sub>0.65</sub> layers can be further supported by the relatively short elongation of RLPs of these two layers along Q (1–10) direction as shown in Figs. 4(a) and 4(b). Smaller dislocation density in [110] (or  $[1\bar{1}0]$ ) direction leads to less diffuse scattering of x-ray in its orthogonal [110] (or [110]) direction, resulting in the shorter elongation of RLPs along Q (1–10) [or Q (110)] in RSMs. Furthermore, it can be found from the asymmetric (115) RSM as shown in Fig. 4(b) that, the In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0.35</sub>Sb<sub>0.65</sub> layers are aligned in a vertical line [fully strained line, red dashed line in Fig. 4(b)] with respect to the In<sub>0.7</sub>Al<sub>0.3</sub>As buffer, which additionally confirmed the pseudomorphic nature of In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0,35</sub>Sb<sub>0,65</sub> layers.<sup>19</sup> Although the in-plane lattice constants of In<sub>0.7</sub>Ga<sub>0.3</sub>As and GaAs<sub>0.35</sub>Sb<sub>0.65</sub> are slightly smaller than that of In<sub>0.7</sub>Al<sub>0.3</sub>As in this p-type TFET structure, the small difference in lattice constant does not generate strain relaxation of these two layers due to the critical layer thickness consideration, which lead to the pseudomorphic nature and low dislocation density within these two layers.

For metamorphic zinc-blende semiconductor structures, the lattice mismatch between substrate and epilayers can be accommodated by dislocation glide. However, asymmetric strain relaxation will lead to different dislocation densities along two orthogonal  $\langle 110 \rangle$  directions, which will in turn result in different lattice constants along [110] and [1 $\bar{1}$ 0] directions. As a result, the anisotropy in strain relaxation states of the TFET structure can be determined by aligning

TABLE I. Summary of strain relaxation properties of the p-channel TEFT structure with incident x-ray beam along [110] and [110] directions.

| Incident beam direction |        | Lattice constant (Å) |        |                |                 |                |               |            |

|-------------------------|--------|----------------------|--------|----------------|-----------------|----------------|---------------|------------|

|                         | Layers | С                    | a      | a <sub>r</sub> | Composition (%) | Relaxation (%) | Tilt (arcsec) | Strain (%) |

| 110                     | GaAsSb | 5.9347               | 5.9127 | 5.9237         | Sb: 62          | 80             | -19           | 0.94       |

|                         | InGaAs | 5.9468               | 5.9162 | 5.9314         | In: 69          | 76             | -38           | 1.07       |

|                         | InAlAs | 5.9649               | 5.9202 | 5.9426         | In: 71          | 70             | -58           | 1.26       |

| [110]                   | GaAsSb | 5.9343               | 5.9132 | 5.9237         | Sb: 62          | 81             | 56            | 0.94       |

|                         | InGaAs | 5.9465               | 5.9146 | 5.9304         | In: 68          | 74             | 35            | 1.05       |

|                         | InAlAs | 5.9648               | 5.9226 | 5.9437         | In: 71          | 72             | 35            | 1.28       |

JVST B - Microelectronics and Nanometer Structures

the projection of the incident x-ray beams along two orthogonal  $\langle 110 \rangle$  directions. Therefore, x-ray RSMs were recorded once again on this structure with the incident x-ray beam along [110] direction and Figs. 5(a) and 5(b) show the symmetric (004) and asymmetric (115) RSMs from this measurement, respectively. The lattice parameters and strain relaxation values extracted from Figs. 5(a) and 5(b) were also summarized in Table I. One can find from Table I that the strain relaxation values of In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers and the In<sub>0.7</sub>Al<sub>0.3</sub>As buffer are almost identical along two orthogonal  $\langle 110 \rangle$  directions, which indicates symmetric strain relaxation of these layers suggests that the total length of misfit dislocations in each  $\langle 110 \rangle$  direction is

Fig. 5. (Color online) (a) Symmetric (004) and (b) asymmetric (115) RSMs of the p-type TFET structure with the incident x-ray beam along [110] direction. The strain relaxation values of  $\rm In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  active layers and the  $\rm In_{0.7}Al_{0.3}As$  buffer are almost identical along two orthogonal  $\langle 110 \rangle$  directions, which indicate symmetric strain relaxation of this structure.

approximately the same. Besides, the lattice tilt amplitude observed from (004) RSMs was less than 200 arc sec from each epilayers in both measurements, indicating nearly equal amount of  $\alpha$  and  $\beta$  dislocations participated during the relaxation process. The small lattice tilt also supports the observed symmetric strain relaxation of the lineally graded  $In_xAl_{1-x}As$  buffer,  $GaAs_{0.35}Sb_{0.65}$  and  $In_{0.7}Ga_{0.3}As$  layers. The symmetric strain relaxation properties not only indicate the homogeneity and effectiveness of the graded buffer on the relaxation of mismatch induced strain, but also provide more flexibility for the alignment of channel direction during the device fabrication with side-wall architecture.<sup>3</sup> As a result, the pseudomorphic nature of In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers and the symmetric strain relaxation of the structure provide a "virtually" defect free and isotropic active region for the p-type TFET structure, which is desirable for improving the performance of TFET devices with low OFFstate leakage and high ON/OFF-ratio.

### B. Surface morphology

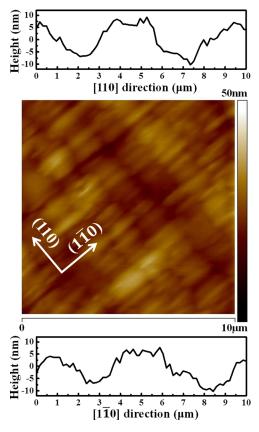

Strain within the linearly graded buffer was primarily relaxed by formation of  $60^{\circ}$  a/2  $\langle 110 \rangle$  {111} misfit dislocations at epilayer/substrate interface. 20 These dislocations can glide along {111} planes<sup>21</sup> and thread toward the surface at  $60^{\circ}$  angle within  $\langle 110 \rangle$  directions,  $^{20,21}$  which results in a cross-hatch pattern on the sample surface. As a result, characterization of the surface morphology is an important metric for the metamorphic TFET structure as it directly relates to the strain relaxation properties. Figure 6 shows the  $10\mu \text{m} \times 10\mu \text{m}$  AFM micrograph of the TFET structure, which displays the anticipated two-dimensional cross-hatch surface morphology. The two-dimensional cross-hatch pattern is well developed and quite uniform with ridges and grooves parallel to [110] and [110] directions, as labeled in the figure. The line profiles in the two orthogonal  $\langle 110 \rangle$ directions are also included in this figure. The uniform distribution of the cross-hatch pattern along [110] and [110] directions suggest a symmetric strain relaxation of the linearly graded buffer layer, which is in agreement with the XRD results. Besides, the AFM measurement shows a smooth surface with a root-mean-square (rms) roughness of 2.58 nm. The well maintained two-dimensional cross-hatch pattern and low surface rms roughness also indicates the low dislocation density of In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers; otherwise, the two-dimensional cross-hatch pattern developed by the graded buffer will be sheltered by high density dislocations and a grainy texture with much higher surface roughness will be expected. 12

#### C. Dislocation and defects

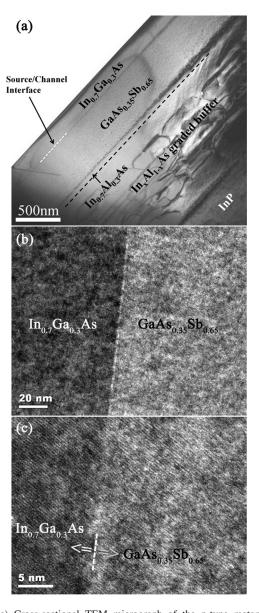

The crystalline quality of the p-type TFET structure was further characterized by cross-sectional TEM. Figure 7(a) shows the bright field cross-sectional TEM micrograph of the TFET structure. All layers were labeled in this figure and the  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterointerface was denoted by an arrow. It can be seen from this figure that the linearly graded  $In_xAl_{1-x}As$  buffer layer effectively accommodates

Fig. 6. (Color online)  $10\mu\mathrm{m}\times10\mu\mathrm{m}$  AFM micrograph of the p-type metamorphic TFET structure. The line profiles in the two orthogonal  $\langle110\rangle$  directions are also included. The uniform distribution of the cross-hatch pattern along [110] and [110] directions suggests a symmetric strain relaxation of the linearly graded buffer layer. The AFM measurement shows a smooth surface morphology of the TFET structure with a root-mean-square (rms) roughness of 2.58 nm.

the lattice mismatch by the formation of dislocations between In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers and the InP substrate. Most of the dislocations were confined within the graded In<sub>x</sub>Al<sub>1-x</sub>As buffer and the upper region of the graded buffer with a thickness of ~200 nm has a minimal dislocation density which cannot be detected at this magnification. As the linearly graded buffer relaxed most of lattice mismatch induced strain, the residual strain within the top of the graded buffer layer is small. No further relaxation took place in this region, leaving a strained and dislocation-free region on the top of the graded buffer, providing a highquality virtual substrate for the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers of the TFET structure. Besides, only one threading dislocation was observed in the In<sub>0.7</sub>Ga<sub>0.3</sub>As/ GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers at this magnification, indicating a threading dislocation density in these layers on the order of  $\sim 10^7/\text{cm}^2$ . Figures 7(b) and 7(c) shows the In<sub>0.7</sub>Ga<sub>0.3</sub>As/ GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface of this p-type TFET structure with high magnification. High contrast at the heterointerface indicates a sharp interface between n<sup>+</sup> In<sub>0.7</sub>Ga<sub>0.3</sub>As source and intrinsic GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel, which is benefited to reduce the effective tunneling barrier width and increase in tunneling current of the TFET device.<sup>22</sup> Besides, no dislocations were observed at the heterointerface from the TEM

Fig. 7. (a) Cross-sectional TEM micrograph of the p-type metamorphic TFET structure. The linearly graded  $\rm In_xAl_{1-x}As$  buffer layer effectively accommodates the lattice mismatch between  $\rm In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  active layers and the InP substrate. Only one threading dislocation was observed in the  $\rm In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  active layers at this magnification, indicating high crystalline quality of the p-type TFET structure. (b) and (c) cross-sectional TEM micrograph of the  $\rm In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterointerface with high magnification. A sharp heterointerface with high crystalline quality was observed.

micrographs with high magnification. The low dislocation density within active layers and the heterointerface suggests high crystalline quality of the p-type TFET structure, which is indispensable for high device performance in fabricated TFETs.

## D. SIMS profiles

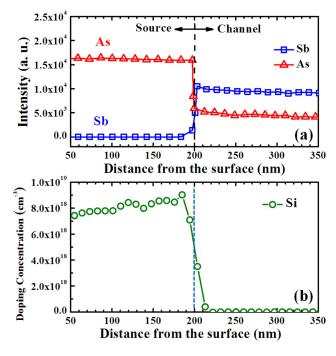

The abruptness of  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  heterojunction as well as the sharpness of Si doping profile is critical to the performance of TFET devices as they directly determine the tunneling barrier width for carrier to transport from source to channel, <sup>22</sup> which directly relates to the ON-

state current of TFETs. Besides, the intermixing of As and Sb at the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> interface will result in uncontrolled layer composition, which will lead to unintended band alignment and may introduce high dislocation density due to compositional mismatch. In order to determine the atomic intermixing of As and Sb as well as the sharpness of Si doping at the source/channel interface, dynamic SIMS measurements were performed to characterize the compositional profiles of As, Sb, and Si in the source and channel regions. Figure 8(a) shows the As, Sb, and Si depth profiles of the p-type TFET structure. The concentration of different elements was not quantified due to the lack of corresponding standards for SIMS measurement. An abrupt In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface was also found in this structure. The transition from As rich In<sub>0.7</sub>Ga<sub>0.3</sub>As to Sb rich GaAs<sub>0.35</sub>Sb<sub>0.65</sub> is less than 10 nm, within the sputter induced broadening of the ion beam, depicting a minimum intermixing between As and Sb at the heterointerface. Figure 8(b) shows the calibrated Si doping profile of the p-type TFET structure. The fluctuation of Si doping profile in the source region may due to the secondary ion beam signal variability in the sputtering process. The dopant abruptness is less than 2 nm/decade from n<sup>+</sup> In<sub>0.7</sub>Ga<sub>0.3</sub>As source to intrinsic GaAs<sub>0.35</sub>Sb<sub>0.65</sub> channel, which is less than the critical dopant abruptness (4 nm/decade)<sup>23</sup> of TFET devices to maximize the junction electric fields and thus enable high ON-state current. The well controlled interface transition with minimum As/Sb intermixing assured the anticipated staggered band alignment with desired effective tunneling barrier height; the abrupt dopant change reduced

Fig. 8. (Color online) (a) Dynamic SIMS depth profiles of As, Sb from the p-type TFET structure. As abrupt As/Sb change with a transition less than 10 nm was confirmed, indicating low level intermixing between As and Sb at the interface. (b) Si doping profile of the p-type TFET structure. An abrupt Si doping profile with the dopant abruptness less than 2 nm/decade suggests a steep junction formed at the source/channel interface.

the carrier tunneling distance and maximized the junction electric field, both of which enhanced high ON-state current.

## E. OFF-state performance and comparison with n-type TFET device structure

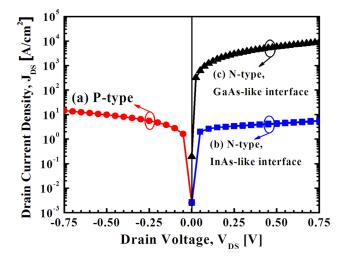

Due to the great challenge of MBE growth of mixed As/ Sb In<sub>x</sub>Ga<sub>1-x</sub>As/GaAs<sub>v</sub>Sb<sub>1-v</sub> heterostructures for p-type staggered gap TFET applications, <sup>12–14</sup> systematically investigation of the structural properties of this heterostructure is essential prior to device fabrication. Studies of growth parameters and optimization of shutter sequences are indispensable for this structure in order to engineer an abrupt change from Sb-rich GaAs<sub>v</sub>Sb<sub>1-y</sub> to As-rich In<sub>x</sub>Ga<sub>1-x</sub>As layer. Otherwise, improper change of group-V fluxes at the In<sub>x</sub>Ga<sub>1-x</sub>As/GaAs<sub>y</sub>Sb<sub>1-y</sub> heterointerface will form a GaAslike heterointerface, which will in turn produce higher dislocation density at the heterointerface and within the In<sub>x</sub>Ga<sub>1-x</sub>As layer. 12,13 These dislocations will introduce fixed charges and change the band alignment from staggered gap to broken gap, resulting in high leakage current of TFET devices. <sup>12</sup> In order to investigate the OFF-state performance of the p-type TFETs, n<sup>+</sup>-i-p<sup>+</sup> diodes were fabricated from this structure. As the OFF-state current of p-type TFETs is governed by the leakage current of the reverse-biased n+-ip<sup>+</sup> diode, <sup>12,22</sup> current–voltage (I-V) characteristics of the n<sup>+</sup>-i-p<sup>+</sup> diode were measured. Figure 9(a) shows the room temperature I-V characteristic of the reverse-biased n<sup>+</sup>-i-p<sup>+</sup> diode. The room-temperature I-V characteristic of the reverse-biased p<sup>+</sup>-i-n<sup>+</sup> diode fabricated from the n-type GaAs<sub>0.35</sub>Sb<sub>0.65</sub>/In<sub>0.7</sub>Ga<sub>0.3</sub>As TFET structure with both (b) InAs-like heterointerface and (c) GaAs-like heterointerface

Fig. 9. (Color online) (a) Room-temperature I-V characteristic of the reverse-biased  $n^+\text{-i-p}^+$  diode fabricated from the p-type  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  TFET structure. The room-temperature I-V characteristic of the reverse-biased  $p^+\text{-i-n}^+$  diode fabricated from the n-type  $GaAs_{0.35}Sb_{0.65}/In_{0.7}Ga_{0.3}As$  TFET structure with both (b) InAs-like heterointerface and (c) GaAs-like heterointerface are also used for comparison. Similar leakage current level of the p-type TFET as that of the N-type TFET with a InAs-like heterointerface indicates that the InAs-like heterointerface with high crystal-line quality was formed at source/channel interface of the p-type TFET structure

are also used for comparison. <sup>12</sup> Similar leakage current level was observed from the p-type TFET as that from the n-type TFET with an InAs-like heterointerface, indicating that an InAs-like interface with high crystalline quality was formed at the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface in the p-type TFET structure. Besides, due to superior material quality, In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> TFETs with an InAs-like heterointerface exhibits 3 orders of magnitude lower leakage current compared with TFETs with a GaAs-like heterointerface [as shown in Fig. 9(c)]. The relatively low leakage current of the p-type TFET supports our structural analysis presented here.

This study demonstrated preferable strain relaxation properties and high crystalline quality of the p-type TFET structure together with minimum ad-atom intermixing at the heterointerface, all of which are necessary for high performance devices. Earlier studies showed that the type-II staggered band alignment with an effective tunneling barrier height  $(E_{\text{beff}} = E_G^{\text{InGaAs}} - \Delta E_V)$  of 0.13 eV was formed at the In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterointerface. <sup>16</sup> This effective tunneling barrier height plays a significant role in the performance of either n-channel 13 or p-channel TFET devices, which not only determines the ON-state band-to-band tunneling current but also sets the blocking barrier for the OFF-state leakage. It has also been reported that high ONstate current of  $135\mu A/\mu m$  with recorded high  $I_{ON}/I_{OFF}$  ratio of  $2.7 \times 10^4$  was achieved in an n-type TFET device using similar In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> heterostructure. <sup>5,11</sup> OFFstate performance studies also confirmed similar leakage current level of this n-type TFET with the p-type TFET structure using in this study. As a result, promising device performance is expected to be achieved in the structure used in this study for complementary p-type TFET applications.

# IV. CONCLUSION

A comprehensive experimental study of the structural properties of a metamorphic In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> p-type tunnel field effect transistor (TFET) structure grown by molecular beam epitaxy was investigated. The experimental results demonstrated high structural quality of this structure. Symmetric (004) and asymmetric (115) x-ray reciprocal space maps revealed the pseudomorphic nature of  $In_{0.7}Ga_{0.3}As/GaAs_{0.35}Sb_{0.65}$  active layers and symmetric strain relaxation along [110] and [110] directions of the structure. Contact mode atomic force microscopy measurement shows an anticipated two-dimensional cross-hatch surface morphology of this structure with a smooth surface root-mean-square roughness of 2.58 nm. Cross-sectional transmission electron microscopy demonstrated that the linearly graded In<sub>x</sub>Al<sub>1-x</sub>As buffer effectively accommodate the lattice mismatch between In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> active layers and the InP substrate. The threading dislocation density within the active region is on the order of  $\sim 10^{\prime}/\text{cm}^2$ , suggesting high crystalline quality of the p-type TFET structure. Dynamic secondary ion mass spectrometry measurement confirmed a low level intermixing between As and Sb atoms as well as an abrupt doping profile at the source/channel junction. The anticipated staggered band alignment with desired effective tunneling barrier height was well maintained due to the pseudomorphic nature of In<sub>0.7</sub>Ga<sub>0.3</sub>As/GaAs<sub>0.35</sub>Sb<sub>0.65</sub> layers as well as the minimum intermixing between As and Sb atoms at the source/channel junction. The superior structural properties and low leakage current density suggest promising device performances of p-type TFETs for high-performance, low standby power, and complementary energy efficient logic application.

## **ACKNOWLEDGMENTS**

This work was supported in part by National Science Foundation under grant number ECCS-1028494 and Intel Corporation.

- <sup>1</sup>A. M. Ionescu and H. Riel, Nature **479**, 329 (2011).

- <sup>2</sup>J. Knoch and J. Appenzeller, *Proceedings of the 63rd IEEE Device Research Conference (DRC)*, (IEEE, New York, 2005), p. 153.

- <sup>3</sup>G. Dewey et al., Proceedings of the IEEE International Electron Devices Meeting (IEDM), (IEEE, New York, 2011), p. 785.

- <sup>4</sup>D. K. Mohata et al., Proceedings of the IEEE International Electron Devices Meeting (IEDM), (IEEE, New York, 2011), p. 781.

- <sup>5</sup>D. Mohata, B. Rajamohanan, T. Mayer, M. Hudait, J. Fastenau, D. Lubyshev, A. W. K. Liu, and S. Datta, IEEE Electron Device Lett. 33, 1568 (2012).

- <sup>6</sup>B. Rajamohanan, D. Mohata, A. Ali, and S. Datta, Appl. Phys. Lett. **102**, 092105 (2013).

- <sup>7</sup>G. Zhou et al., IEEE Conference Proceedings of the International Electron Devices Meeting (IEDM), (IEEE, New York, 2012), p. 777.

- <sup>8</sup>A. W. Dey et al., IEEE Conference Proceedings of the Device Research Conference (DRC), (IEEE, New York, 2012), p. 205.

- <sup>9</sup>G. Zhou *et al.*, IEEE Electron Device Lett. **33**, 782 (2012).

- <sup>10</sup>H. Zhao, Y. Chen, Y. Wang, F. Zhou, F. Xue, and J. Lee. IEEE Electron Device Lett. 31 1392 (2010).

- <sup>11</sup>D. K. Mohata *et al.*, *IEEE Symposium on VLSI Technology (VLSI)* (IEEE, New York, 2012), p. 53.

- <sup>12</sup>Y. Zhu et al., J. Appl. Phys. **112**, 024306 (2012).

- <sup>13</sup>Y. Zhu *et al.*, J. Appl. Phys. **112**, 094312 (2012).

- <sup>14</sup>Y. Zhu, N. Jain, D. K. Mohata, S. Datta, D. Lubyshev, J. M. Fastenau, A. K. Liu, and M. K. Hudait, J. Appl. Phys. 113, 024319 (2013).

- <sup>15</sup>Y. Zhu, D. K. Mohata, S. Datta, and M. K. Hudait, IEEE Trans. Device Mater. Rel. PP, 1 (2013).

- <sup>16</sup>Y. Zhu, N. Jain, D. K. Mohata, S. Datta, D. Lubyshev, J. M. Fastenau, A. K. Liu, and M. K. Hudait, Appl. Phys. Lett. **101**, 112106 (2012).

- <sup>17</sup>M. K. Hudait, Y. Zhu, N. Jain, S. Vijayaraghavan, A. Saha, T. Merritt, and G. A. Khodaparast, J. Vac. Sci. Technol. B 30, 051205 (2012).

- <sup>18</sup>E. A. Fitzgerald, A. Y. Kim, M. T. Currie, T. A. Langdo, G. Taraschi, and M. T. Bulsara, Mater. Sci. Eng. B 67, 53 (1999).

- <sup>19</sup>J. M. Chauveau, Y. Androussi, A. Lefebvre, J. Di Persio, and Y. Cordier, J. Appl. Phys. 93, 4219 (2003).

- <sup>20</sup>M. K. Hudait, Y. Lin, M. N. Palmisiano, C. Tivarus, J. P. Pelz, and S. A. Ringel, J. Appl. Phys. **95**, 3952 (2004).

- <sup>21</sup>M. Natali, F. Romanato, E. Napolitani, D. De Salvador, and A. V. Drigo, Phys. Rev. B 62, 11054 (2000).

- <sup>22</sup>Y. Zhu and M. K. Hudait, Nanotechnol. Rev. **0**, 1 (2013).

- <sup>23</sup>A. C. Seabaugh and Q. Zhang, Proc. IEEE **98**, 2095 (2010).