The Pennsylvania State University

The Graduate School

Department of Electrical Engineering

## DESIGN, FABRICATION AND CHARACTERIZATION OF

## ANTIMONIDE MOS TRANSISTORS

A Dissertation in

Electrical Engineering

by

Ashkar A. Ali

© 2012 Ashkar A. Ali

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2012

The dissertation of Ashkar Ali Aliyaru Kunju was reviewed and approved\* by the following:

Suman Datta Professor of Electrical Engineering and Materials Research Institute Dissertation Advisor Chair of Committee

Peter Schiffer Associate Vice President for Research Director of Strategic Initiatives Professor of Physics

Suzanne Mohney Professor of Materials Science and Engineering and Professor of Electrical Engineering

Theresa Mayer Distinguished Professor of Electrical Engineering

Vijay Narayanan Professor of Computer Science and Engineering and Professor of Electrical Engineering

Jerzy Ruzyllo Distinguished Professor of Electrical Engineering

Kultegin Aydin Professor of Electrical Engineering Head of the Department of Electrical Engineering

\*Signatures are on file in the Graduate School

### ABSTRACT

Future transistor scaling will require enhancement in device electrostatics (multigate), channel transport enhancement (beyond strained Silicon) and reduction in parasitics (contact, junction engineering etc.). Due to the high electron mobility and hole mobility (using strain), antimony (Sb) based III-V materials are of strong interest as channel material for low power all-antimonide complementary metal-oxide-semiconductor (CMOS) digital logic. Sb-based MOSFETs can operate at high speed and very low supply voltage, which promises to dramatically lower the power dissipation in future high-speed logic circuits.

This dissertation will describe compound semiconductor based transistor architecture which integrates mixed anion InAs<sub>x</sub>Sb<sub>1-x</sub> quantum-wells (QW) exhibiting very high electron mobility, for ultra-low power logic applications. I will discuss the following aspects of the n-channel Sb MOSFETs using experimental data and detailed modeling: a) material selection and device design; b) strategy for integrating a high-k dielectric using a composite barrier scheme; c) equivalent oxide thickness scalability including quantum capacitance; and d) transport properties in long and short channel Sb NMOSFETs. The dissertation concludes with benchmarking the performance of Sb NMOSFETs with other III-V devices, and address the feasibility of Sb NMOSFETs for enhancement mode (normally OFF) logic transistors operating with ultra low energy dissipation.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                   | vi                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                    | xii                                    |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                  | xiii                                   |

| Chapter 1 Antimonide NMOSFET Device Design for Ultra-low Power Logic Applications                                                                                                                                                                                                                                                                                 | 1                                      |

| I. Motivation: Unified Material System with High Electron and Hole Mobility<br>II. Device Architecture of Sb QW MOSFET for Ultra-low $V_{DD}$ Logic<br>III. Device Layer Design and Characterization                                                                                                                                                              | 6                                      |

| Chapter 2 Dielectric Integration Strategy                                                                                                                                                                                                                                                                                                                         | 13                                     |

| <ul> <li>I. Introduction</li> <li>II. GaSb MOS Capacitor Fabrication</li></ul>                                                                                                                                                                                                                                                                                    | 15<br>15<br>16<br>16<br>22<br>24<br>27 |

| Chapter 3 Antimonide MOSFET Fabrication and Characterization                                                                                                                                                                                                                                                                                                      |                                        |

| <ul> <li>I. Introduction</li> <li>II. Device Fabrication</li> <li>III. Results and Discussion</li> <li>Development of a Scaled Gate Stack for Antimonide MOSFETs</li> <li>DC Characterization</li> <li>Long Channel Device Characterization</li> <li>Short Channel Device Characterization</li> <li>Enhancement Mode Operation</li> <li>IV.Conclusions</li> </ul> | 32<br>34<br>34<br>34<br>37<br>41<br>45 |

| Chapter 4 Quantum Capacitance and Gate Capacitance Scalability of Sb NMOSFETs                                                                                                                                                                                                                                                                                     | 54                                     |

| <ul> <li>I. Introduction</li> <li>II. Experimental C<sub>g</sub>-V<sub>g</sub> Measurements and Correcting for D<sub>it</sub></li> <li>Fundamentals of Interface States Characterization</li> <li>Equivalent Circuit Modeling for D<sub>it</sub> Characterization</li> <li>III. Analytical Modeling of Gate Capacitance of QW-MOSFET Including Non-</li> </ul>    | 56<br>57<br>64                         |

| parabolicity<br>IV.Shubnikov-de Haas Analysis for Effective Mass Extraction<br>V. Gate Capacitance Scaling Projection                                                                                                                                                                                                                                             | 75                                     |

| VI.Conclusions                                              | 83 |

|-------------------------------------------------------------|----|

| Chapter 5 Future Works: P-channel Antimonide MOSFETs        | 85 |

| I. Summary on N-channel Antimonide MOSFETs                  |    |

| II. P-channel Antimonide MOSFETs<br>III.Future works        |    |

| Appendix: Process Flow for Antimonide QW MOSFET Fabrication | 91 |

| Bibliography                                                | 98 |

# LIST OF FIGURES

| Figure 1-1. Power dissipation in CPU for various technologies as a function of the year of introduction (Source: Intel [3])                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2. Transistor operating voltage range showing energy efficient computation for near threshold voltage operation. (Source: Intel Labs ISSCC [5])                                                                                                          |

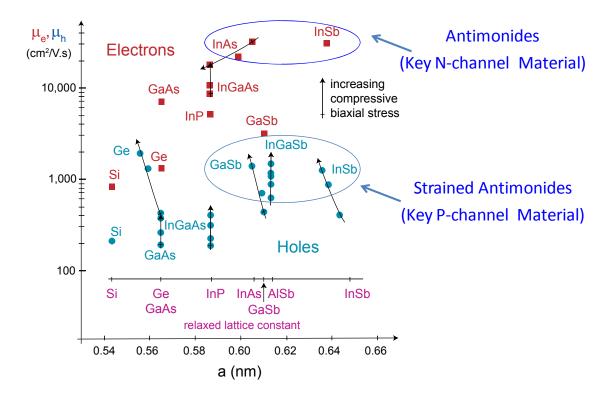

| Figure 1-3. Electron and hole mobility of various III-V compound semiconductors (Source: del Alamo MIT [1]). Antimonides are very attractive since they have high electron as well as high hole mobility                                                          |

| Figure 1-4. Electron mobility of InAsSb QW heterostructure layers compared to that of Si NMOS inversion mobility and the hole mobility of InGaSb QW layers compared to that of Si PMOS inversion layers                                                           |

| Figure 1-5. Schematic showing integration of InAsSb NMOS and InGaSb PMOS for III-<br>V complementary logic operation                                                                                                                                              |

| Figure 1-6. TEM micrographs of the InAs <sub>0.8</sub> Sb <sub>0.2</sub> QWFET stack grown on GaAs by MBE and the defect free active device layers                                                                                                                |

| Figure 1-7. Schematic of the Sb QW MOSFET device layers                                                                                                                                                                                                           |

| Figure 1-8. TEM micrographs of the InAs <sub>0.8</sub> Sb <sub>0.2</sub> QWFET stack grown on GaAs by MBE and the defect free active device layers                                                                                                                |

| Figure 1-9. Energy band diagram of the InAsSb QWFET device layers showing carriers confined effectively in the QW with no carrier spill over to the barrier layer9                                                                                                |

| Figure 1-10. Quantitative mobility spectrum analysis (QMSA) for the QW heterostructure obtained using magneto-conductance measurements at various temperatures and under varying magnetic field                                                                   |

| Figure 1-11. Hall mobility of the Sb QW device layer as a function of temperature from 4K-300K                                                                                                                                                                    |

| Figure 1-12. (a) Parameters used for modeling the different scattering mechanisms (b) Percentage contribution of different scattering mechanisms to the $1/\mu$ at room temperature showing the mobility is limited by Coulomb scattering due to interface charge |

| Figure 2-1. Optical micrograph of device layers after HCl surface treatment step on, (a) sample without GaSb cap (top InAlSb barrier layer is exposed to HCl), and (b) sample with GaSb cap                                                                       |

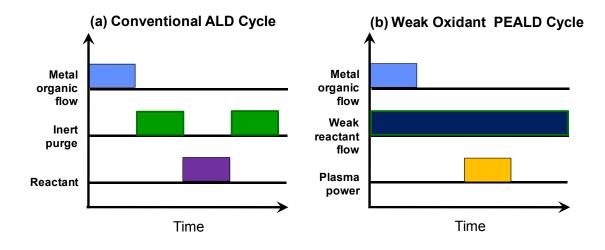

| Figure 2-2. Schematic of (a) conventional ALD process with a strong reactant, and (b)<br>Weak oxidant PEALD process with a pulsed plasma sequence to form the oxide                                                                                                                                           | 16 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

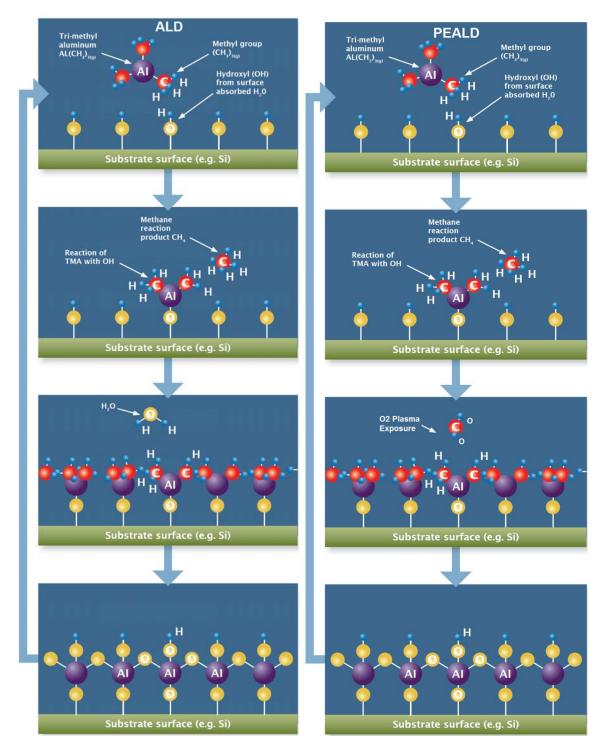

| Figure 2-3. Schematic illustration of the thin film deposition process using ALD and PEALD (Source: Cambridge Nanotech Corporate Brochure June 2010.)                                                                                                                                                         | 17 |

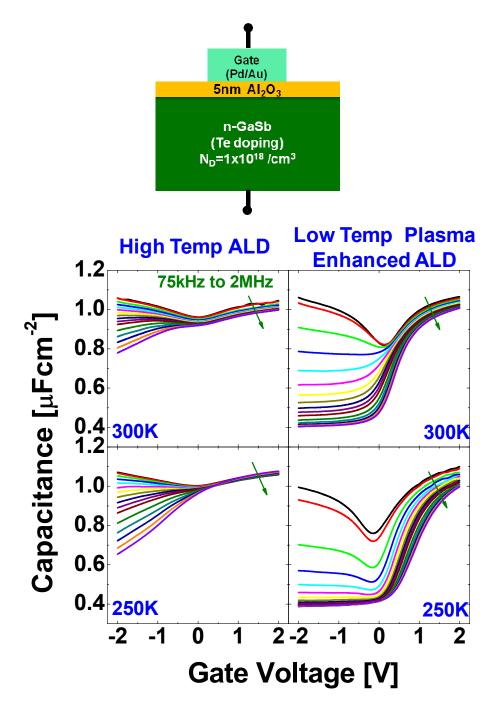

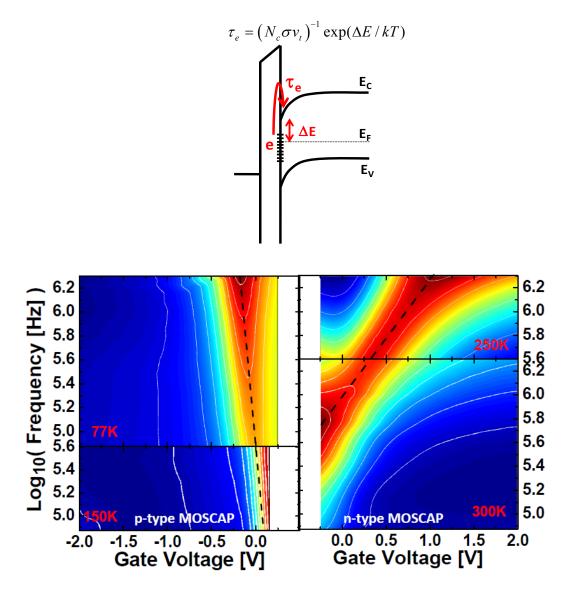

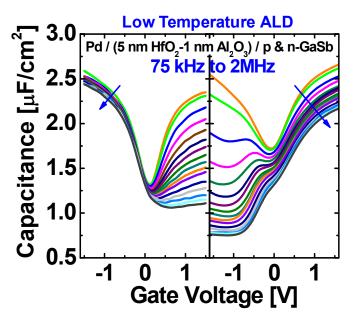

| Figure 2-4. <i>C-V</i> characteristics as a function of frequency of n-type ALD and PEALD MOS capacitors with HCl treatment. Measurement temperature is indicated in the figure.                                                                                                                              | 19 |

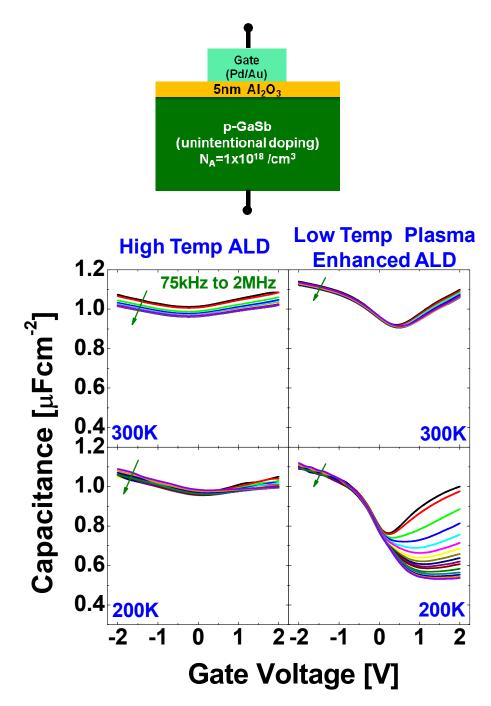

| Figure 2-5. <i>C-V</i> characteristics as a function of frequency of p-type ALD and PEALD samples with HCl treatment. Measurement temperature is indicated in the figure                                                                                                                                      | 20 |

| Figure 2-6. Conductance $(G/\omega)$ contours of n-type and p-type GaSb MOSCAPs with PEALD Al <sub>2</sub> O <sub>3</sub> showing good Fermi level modulation towards valence and conduction band sides.                                                                                                      | 21 |

| Figure 2-7. XPS data comparing the concentration of $Sb_2O_3$ in ALD and PEALD samples. Reduction of $Sb_2O_3$ in the (higher temperature) ALD samples is evident                                                                                                                                             | 23 |

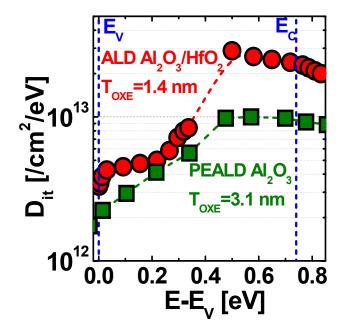

| Figure 2-8. Extracted $D_{it}$ from multi-temperature <i>C-V/G-V</i> analysis of n and p type GaSb MOSCAPs showing low $D_{it}$ near $E_V$ for PEALD Al <sub>2</sub> O <sub>3</sub> /GaSb interface. Fermi level movement at the GaSb interface for the range of operation of the Sb QW MOSFET is also shown. | 25 |

| Figure 2-9. Fermi level movement efficiency of GaSb MOSCAPs with ALD and PEALD Al <sub>2</sub> O <sub>3</sub>                                                                                                                                                                                                 | 25 |

| Figure 2-10. <i>C-V</i> of n and p type GaSb MOS capacitors with 1nm Al <sub>2</sub> O <sub>3</sub> - 5.5 nm HfO <sub>2</sub> dielectric stack deposited using low temperature (250 C) ALD process                                                                                                            | 26 |

| Figure 2-11. Extracted $D_{it}$ from multi-temperature C-V/G-V analysis of n-type and p-type GaSb MOSCAPs showing low $D_{it}$ near valence band for both low temperature ALD and low temperature PEALD process.                                                                                              | 27 |

| Figure 2-12. O 1s energy-loss spectrum for 20 nm Al <sub>2</sub> O <sub>3</sub> film. The inset is a magnified region of the energy loss spectrum.                                                                                                                                                            | 28 |

| Figure 2-13. Valence band spectra of Al <sub>2</sub> O <sub>3</sub> and GaSb (More details of the band offset determination procedure is reported in [25]                                                                                                                                                     |    |

| Figure 2-14. Schematic band alignment of Al <sub>2</sub> O <sub>3</sub> with GaSb                                                                                                                                                                                                                             | 29 |

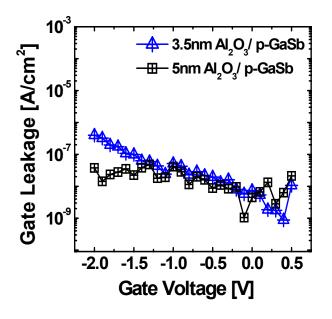

| Figure 2-15. Gate leakage of GaSb MOS capacitors with Al <sub>2</sub> O <sub>3</sub>                                                                                                                                                                                                                          | 29 |

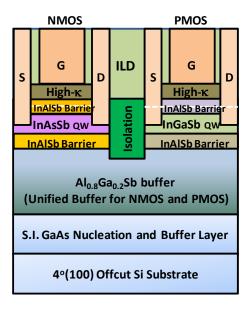

| Figure 3-1. Schematic of Sb CMOS with common buffer technology, highlights the vision of low power, high speed Sb CMOS                                                                                                                                                                                        | 32 |

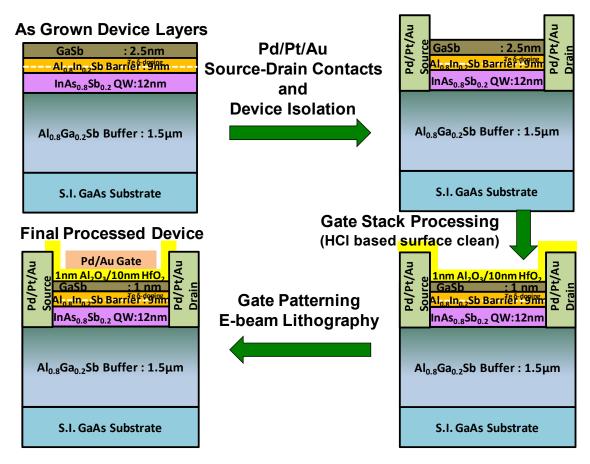

| Figure 3-2. Schematic showing the process flow for fabricating the Sb NMOSFET                                                                                                                                                                                                                                 | 33 |

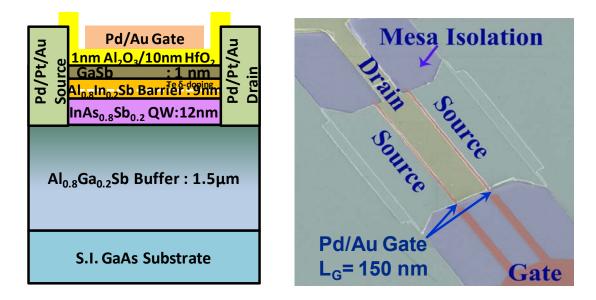

| Figure 3-3. Schematic of the Sb NMOS with $1nmAl_2O_3/10nm$ HfO <sub>2</sub> dielectric, and tilted view SEM image of the fabricated device with 150nm L <sub>G</sub> and 500nm source-to-drain spacing                                                                                     | 33 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

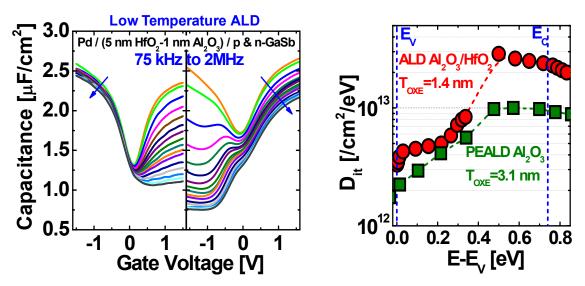

| Figure 3-4. <i>C-V</i> of n and p type GaSb MOS capacitors with 1nm $Al_2O_3$ - 5.5 nm HfO <sub>2</sub> dielectric stack deposited using low temperature (250 °C) ALD process, and the Extracted $D_{it}$ from multi-temperature <i>C-V/G-V</i> analysis of n-type and p-type GaSb MOSCAPs. | 34 |

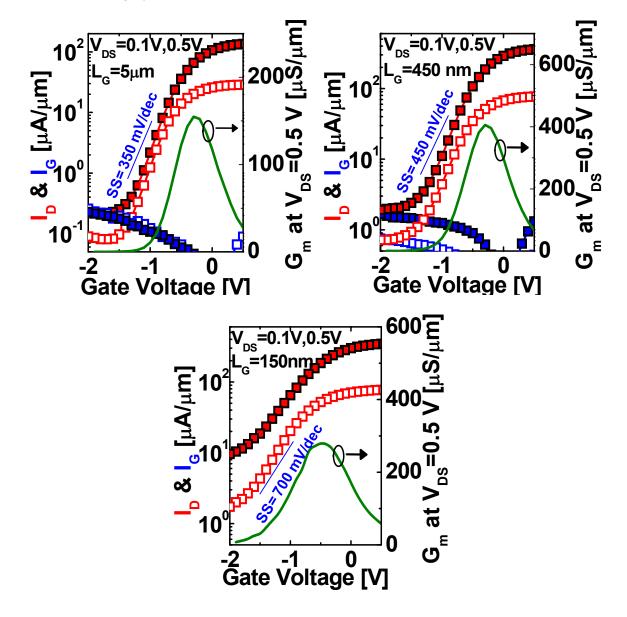

| Figure 3-5. Transfer characteristics of Sb nMOSFETs with 150nm, 450nm and 5µm gate lengths                                                                                                                                                                                                  | 35 |

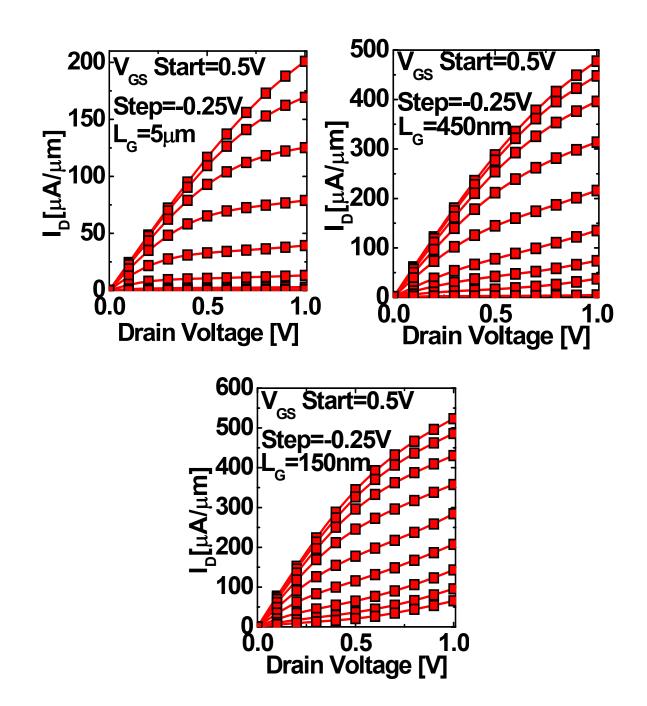

| Figure 3-6. Output characteristics of Sb nMOSFETs with 150nm, 450nm and 5µm gate lengths                                                                                                                                                                                                    | 36 |

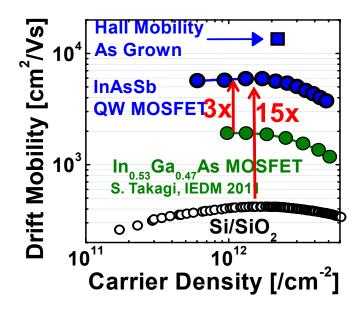

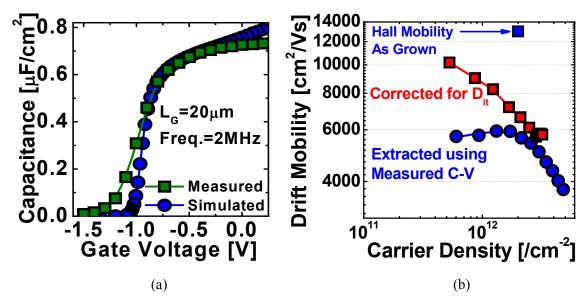

| Figure 3-7. Extracted drift mobility vs $N_s$ showing record high mobility                                                                                                                                                                                                                  | 37 |

| Figure 3-8. (a) Measured and modeled split C-V characteristics, and (b) Drift mobility extracted using measured $C-V$ characteristics and the corrected mobility accounting for stretch-out due to $D_{it}$                                                                                 | 38 |

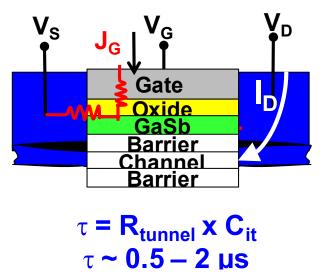

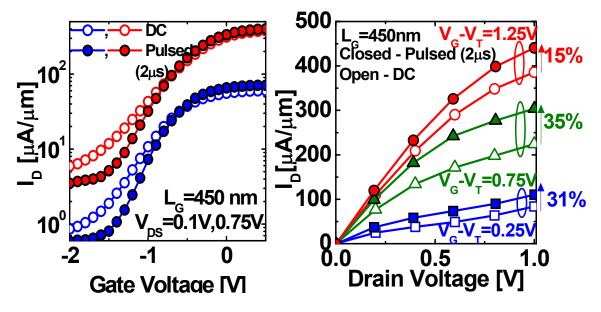

| Figure 3-9. Schematic showing traps at the oxide GaSb interface capturing electrons from the gate leakage current. Estimated trap response time is in the range of 0.5 to 2µs                                                                                                               | 39 |

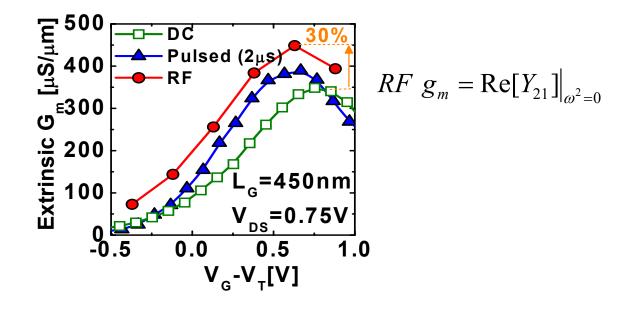

| Figure 3-11. Extrinsic RF $g_m$ showing 30% enhancement over DC $g_m$ due to less charge trapping in RF.                                                                                                                                                                                    | 40 |

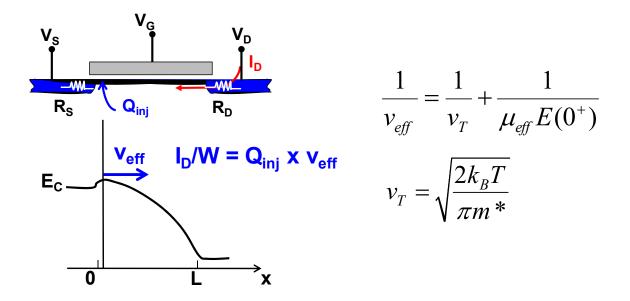

| Figure 3-12.Effective injection velocity of electrons at the top of the barrier determines current in a short channel MOSFET                                                                                                                                                                | 41 |

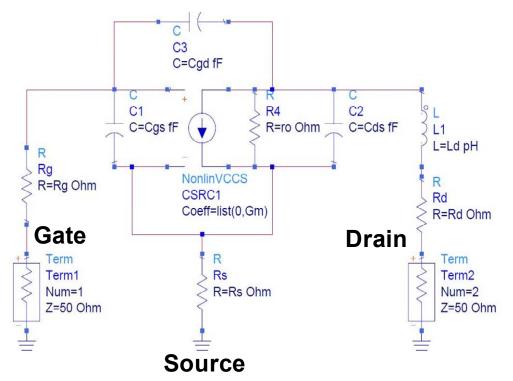

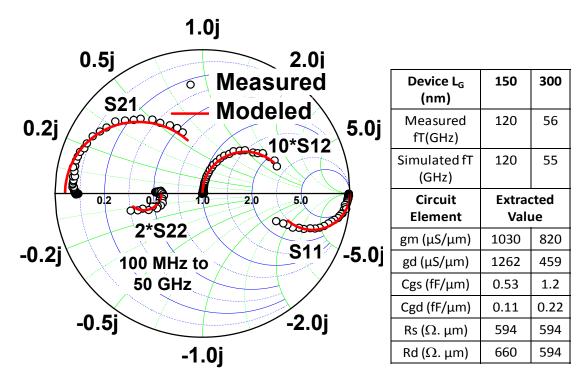

| Figure 3-13. A simplified MOSFET small signal equivalent circuit which was used to model the measured s-parameters of Sb NMOSFET                                                                                                                                                            | 42 |

| Figure 3-14. Measured and modeled S-parameters of the 150nm $L_G$ Sb NMOS at $V_G-V_T=$ 0.6V and $V_{DS}=0.75V$ , and the extracted circuit elements from the small signal model .                                                                                                          | 43 |

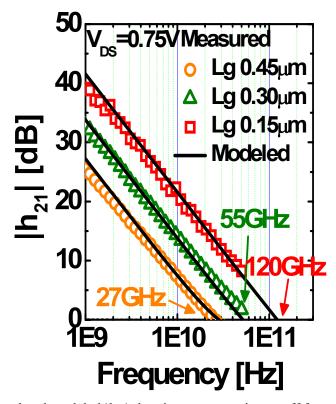

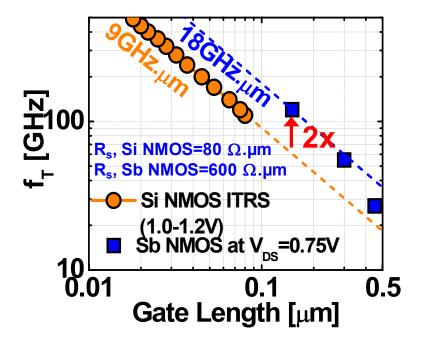

| Figure 3-15. Measured and modeled $ h_{21} $ showing current gain cut-off frequency $(f_i)$ of 120 GHz, 55 GHz, 27 GHz for Sb NMOSFETs with 150 nm, 300 nm and 450 nm gate lengths                                                                                                          | 44 |

| Figure 3-16. Cut-off frequency $(f_t)$ vs gate length for Sb compared to Si NMOSFETs.<br>The measured $f_T$ , and $f_T \times L_G$ are the highest reported in literature among III-V MOSFETs.                                                                                              | 44 |

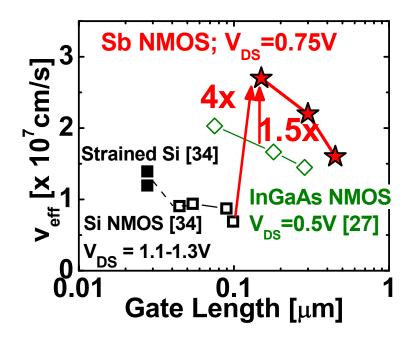

| Figure 3-17. Extracted source injection velocity as a function of gate length for Sb NMOSFET                                                                                                                                                                                                | 45 |

| Figure 3-18. Schematic of the enhancement mode device structure with scaled barrier and quantum well.                                                                                                                                                                                       | 46 |

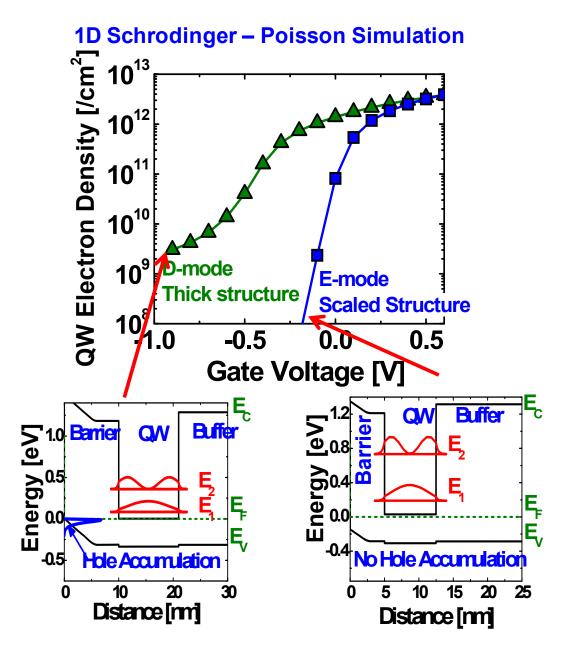

| Figure 3-19. 1D Schrodinger-Poisson simulation showing enhanced electrostatic coupling of the gate to the quantum well. Band diagram in the OFF-state for the D-mode and E-mode shows less potential drop in barrier for scaled E-mode. This avoids hole accumulation in the barrier layer in the OFF-state of E-mode device and reduces I <sub>OFF</sub> | 7 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

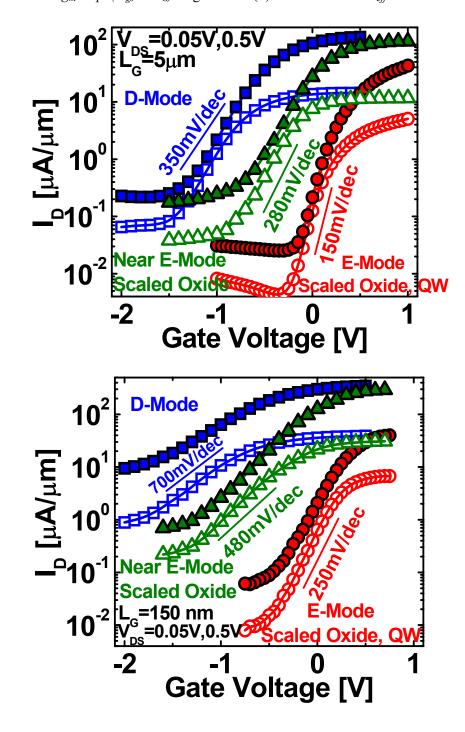

| Figure 3-20. Transfer characteristics of long channel ( $L_G=5 \mu m$ ) and short channel ( $L_G=150 nm$ ) Sb nMOSFETs for D-mode (thick oxide and QW), near E-mode (scaled oxide) and E-mode (scaled oxide and QW) device structures                                                                                                                     | 9 |

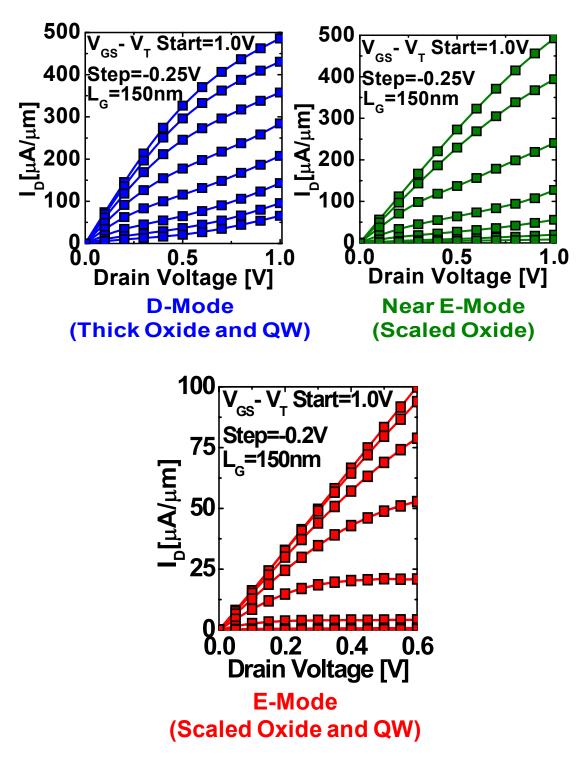

| Figure 3-21. Output characteristics of short channel (L <sub>G</sub> =150 nm) Sb nMOSFETs for D-<br>mode (thick oxide and QW), near E-mode (scaled oxide), and E-mode (scaled oxide<br>and QW) device structures                                                                                                                                          | 0 |

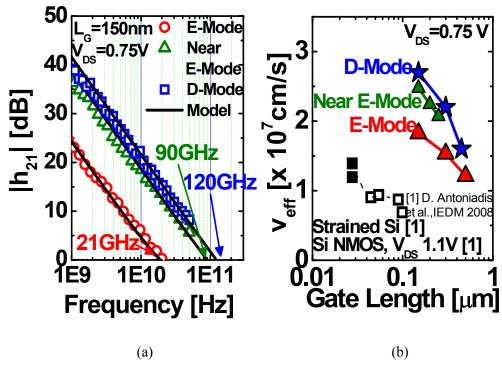

| Figure 3-22. (a) Current gain vs frequency, and (b) Source injection velocity as a function of gate length for D-Mode, Near E-mode and E-Mode Sb NMOSFET5                                                                                                                                                                                                 | 1 |

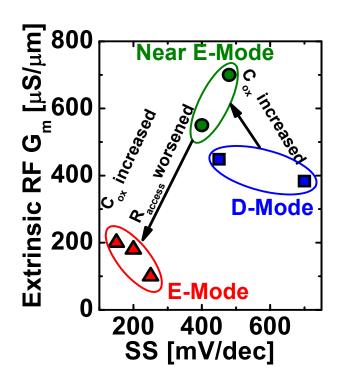

| Figure 3-23. Peak extrinsic RF $g_m$ for D-mode, near E-mode and E-mode devices vs sub-<br>threshold slope                                                                                                                                                                                                                                                | 2 |

| Figure 4-1. Schematic of the InAs <sub>0.8</sub> Sb <sub>0.2</sub> QW-MOSFET with composite high-k dielectric (10 nm nm HfO <sub>2</sub> – 1 nm Al <sub>2</sub> O <sub>3</sub> – 1 nm GaSb)                                                                                                                                                               | 6 |

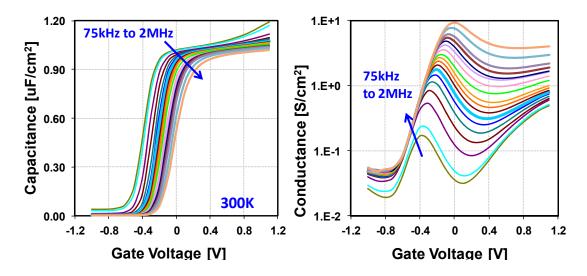

| Figure 4-2. Measured split capacitance $(C_g - V_g)$ and conductance $(G - V_g)$ characteristics of InAs <sub>0.8</sub> Sb <sub>0.2</sub> QW-MOSFET at 300K                                                                                                                                                                                               | 7 |

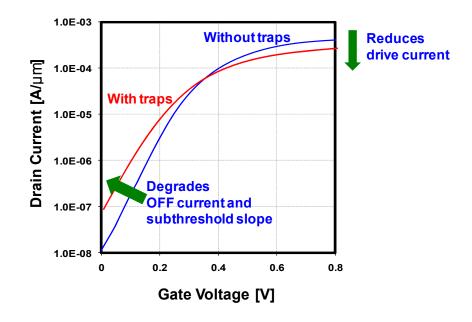

| Figure 4-3. Transfer characteristics of an nMOSFET showing the impact of $D_{it}$ . Charging of traps gives rise to poor sub-threshold slope, degraded OFF state leakage and poor ON current                                                                                                                                                              | 8 |

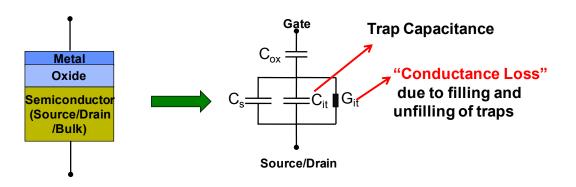

| Figure 4-4. Equivalent ciruit model of a MOS capacitor with D <sub>it</sub> at the oxide-<br>semiconductor interface                                                                                                                                                                                                                                      | 8 |

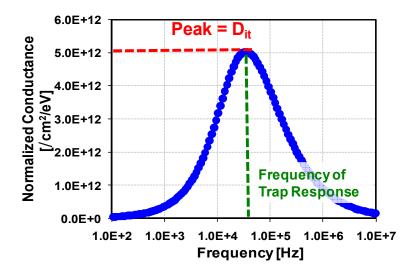

| Figure 4-5. <i>D<sub>it</sub></i> extraction using conductance method proposed by Nicollian and Brews [49]                                                                                                                                                                                                                                                | 9 |

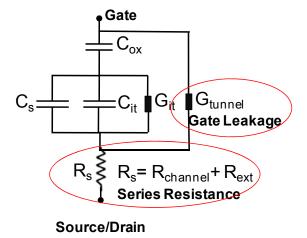

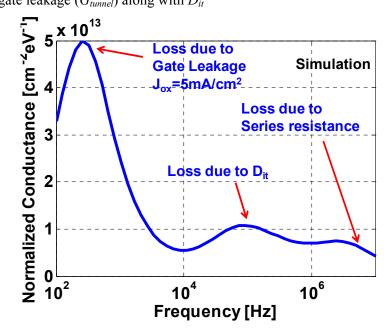

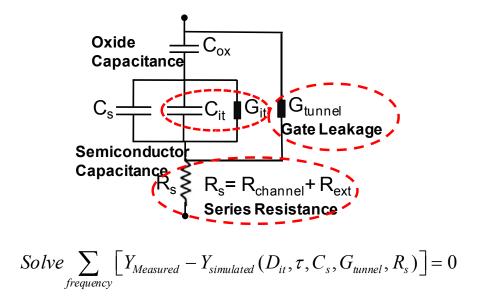

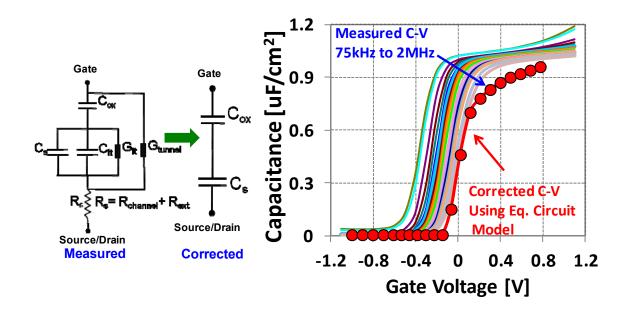

| Figure 4-6. Equivalent circuit model for a MOSFET including the effects of series resistance ( $R_{series}$ ) and gate leakage ( $G_{tunnel}$ ) along with $D_{it}$                                                                                                                                                                                       | 0 |

| Figure 4-7. Normalized conductance as a function of frequency showing conductance peaks due to $D_{it}$ , gate leakage and series resistance                                                                                                                                                                                                              | 0 |

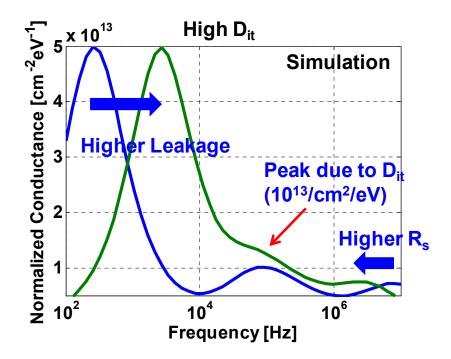

| Figure 4-8. Normalized conductance as a function of frequency showing effects of increased gate leakage and series resistance for high $D_{it}$ (1x10 <sup>13</sup> /cm <sup>2</sup> /eV) case6                                                                                                                                                           | 1 |

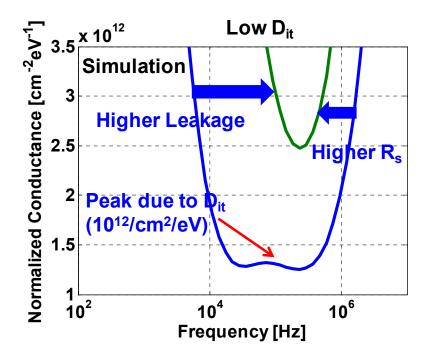

| Figure 4-9. Normalized conductance as a function of frequency showing effects of increased gate leakage and series resistance for high $D_{it}$ (1x10 <sup>13</sup> /cm <sup>2</sup> /eV) case62                                                                                                                                                          | 2 |

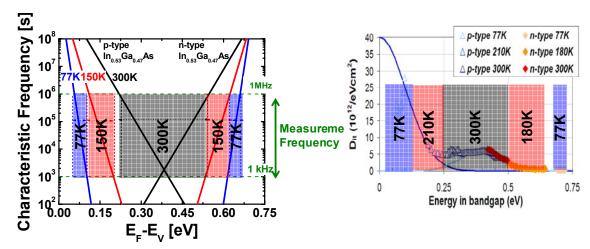

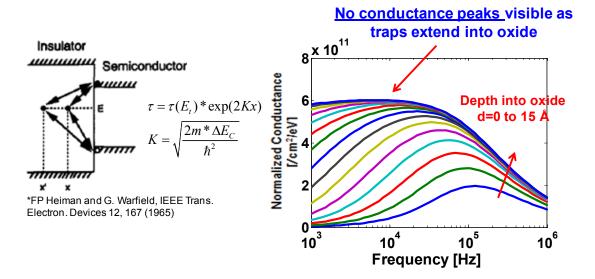

| Figure 4-10. Characteristics frequency of trap response as a function of position in the band gap. $D_{it}$ extraction using conductance method requires multi-temperature measurements to scan the band gap. A typical $D_{it}$ profile of In <sub>0.53</sub> Ga <sub>0.47</sub> As semiconductor with Al <sub>2</sub> O <sub>3</sub> gate dielectric obtained using conductance analysis is shown on the right with the different measurement temperatures indicated along the band gap [50].                                   | 3 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 4-11. Normalized conductance as a function of frequency for traps which extend physically into the oxide                                                                                                                                                                                                                                                                                                                                                                                                                   | 3 |

| Figure 4-12. Equivalent circuit model for self-consistently solving the measured capacitance and conductance                                                                                                                                                                                                                                                                                                                                                                                                                      | 4 |

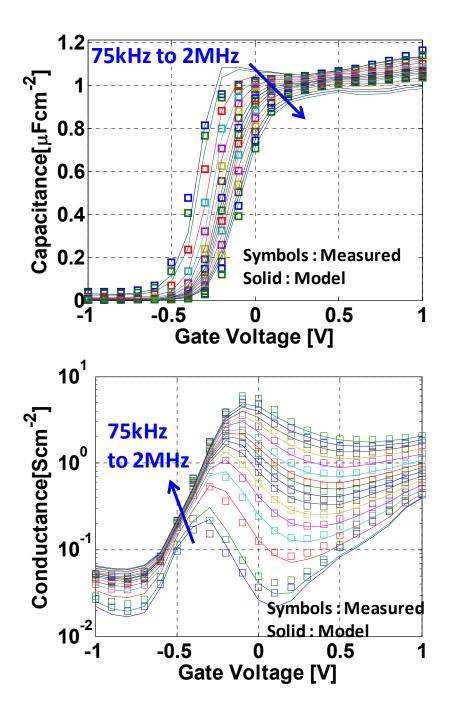

| Figure 4-13. Self consistent solving of capacitance and conductance data at 300K using the equivalent circuit model, showing excellent fit between measured and modeled data                                                                                                                                                                                                                                                                                                                                                      | 6 |

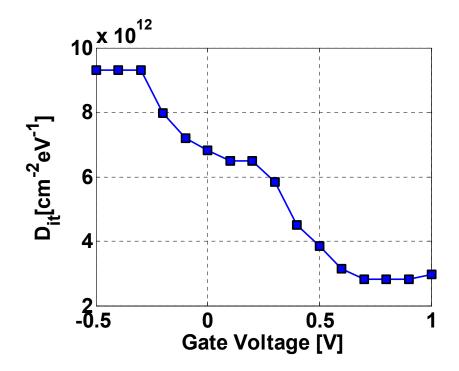

| Figure 4-14. Extracted $D_{it}$ as a function of gate voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 |

| Figure 4-15. $C_g$ - $V_g$ curves corrected for $D_{it}$ along with the measured $C_g$ - $V_g$ characteristics6                                                                                                                                                                                                                                                                                                                                                                                                                   | 7 |

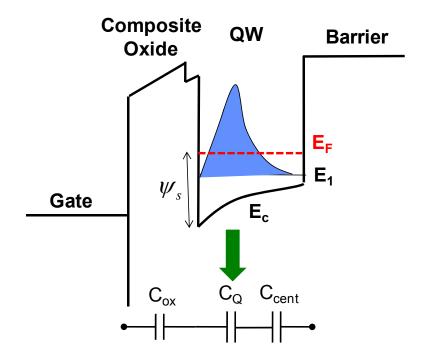

| Figure 4-16. Schematic of electron distribution in the Sb QW MOSFET. The semiconductor capacitance depends on the density of states (quantum capacitance, $C_Q$ ) as well as the change in sub-bands with field in the quantum well (centroid capacitance $C_{cent}$ , which is associated with the distribution of electrons in the QW)6                                                                                                                                                                                         | 9 |

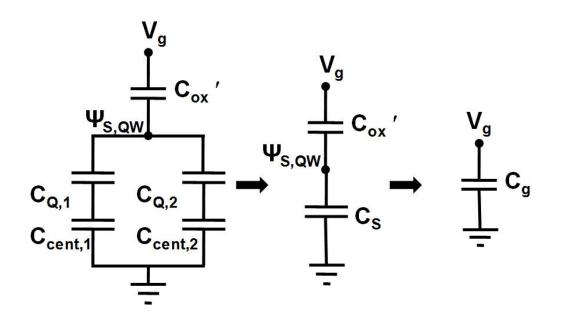

| Figure 4-17. Equivalent circuit model of a QW-MOSFET showing the different components of gate capacitance. $C_{Q,i}$ stands for quantum capacitance of the <i>i</i> -th subband, $C_{cent,i}$ stands for centroid capacitance of the <i>i</i> -th subband, $C_{ox}$ stands for the series combination of oxide and barrier capacitance and $\Psi_{S,QW}$ stands for the quantum well potential. Only two subbands are considered in the model                                                                                     | 1 |

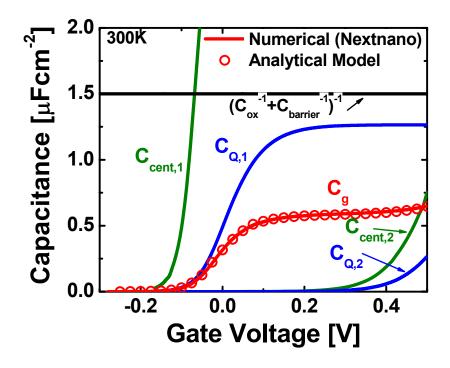

| Figure 4-18. Analytical modeling of gate capacitance of InAs <sub>0.8</sub> Sb <sub>0.2</sub> QW-MOSFET compared with numerical simulations (Nextnano)                                                                                                                                                                                                                                                                                                                                                                            | 2 |

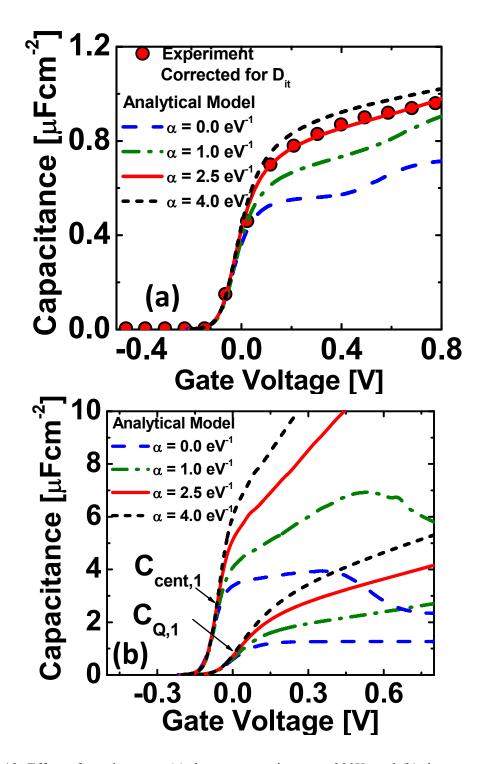

| Figure 4-19. Effect of varying $\alpha$ on (a) the gate capacitance at 300K, and (b) the quantum and centroid capacitance at 300K. The kink visible in the CV curves in (a) for $\alpha$ =0 and 1, is due to capacitance contributions from the second sub-band. Capacitance components of the second sub band are not shown in (b) for clarity. The drop in centroid capacitance for $\alpha$ =0 and 1 in (b) is also due to second subband population. Best fit to the experimental data was obtained with $\alpha$ =2.5 $eV^1$ | 3 |

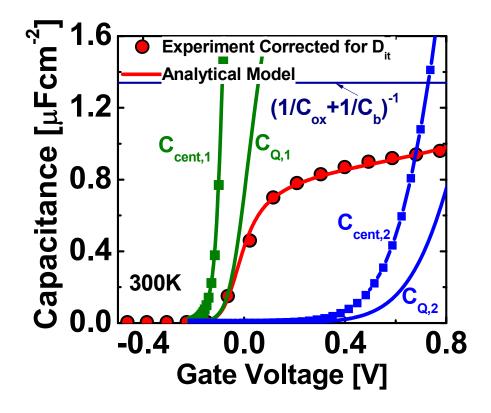

| Figure 4-20. Components of the gate capacitance for the 300K $C_g$ - $V_g$ data7                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 |

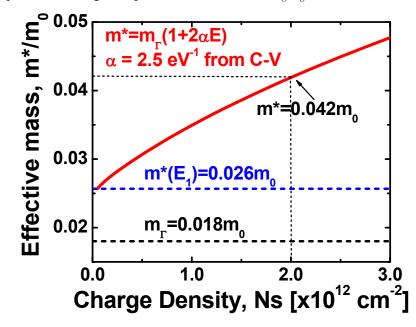

| Figure 4-21. Effective mass extracted from the $C_g$ - $V_g$ analysis as a function of charge density in the QW                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 |

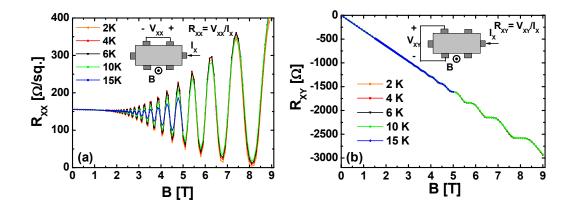

| Figure 4-22. Measured sheet resistance $(R_{XX})$ and (b) Hall resistance $(R_{XY})$ of the InAs <sub>0.8</sub> Sb <sub>0.2</sub> QW-heterostructure from 0-9 tesla. Insets in the figures show the configurations employed to measure $R_{XX}$ and $R_{XY}$                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

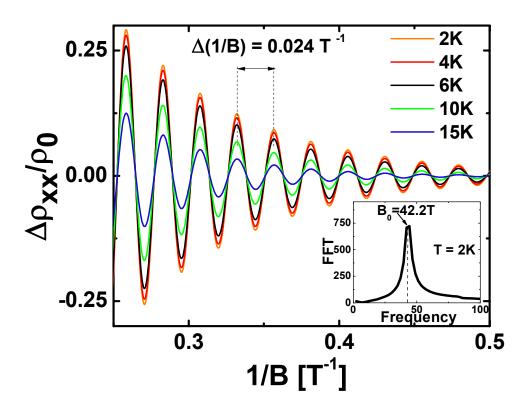

| Figure 4-23. Periodic SdH oscillations in $\Delta \rho_{\chi\chi}/\rho_0$ (after removing the background                                                                                                                                                                                                                                                                                                                                                                       |

| contribution) as a function of <i>1/B</i> . Fast Fourier Transform (FFT) of $\Delta \rho_{XX} / \rho_0$ vs                                                                                                                                                                                                                                                                                                                                                                     |

| <i>1/B</i> is shown in the inset                                                                                                                                                                                                                                                                                                                                                                                                                                               |

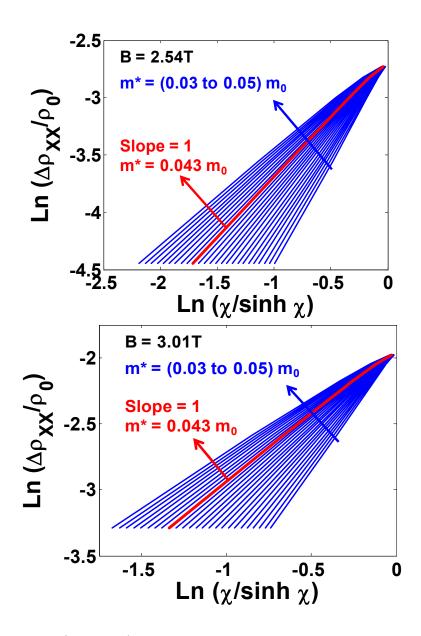

| Figure 4-24. Plot of $Ln \left( \frac{\Delta \rho_{XX}}{\rho_0} \right)$ vs $Ln \left( \frac{\chi}{\sinh \chi} \right)$ for (a) B=2.54T, and (b) B=3.01T to                                                                                                                                                                                                                                                                                                                    |

| extract effective mass. Correct value of effective mass gives a slope of 1 for the graph                                                                                                                                                                                                                                                                                                                                                                                       |

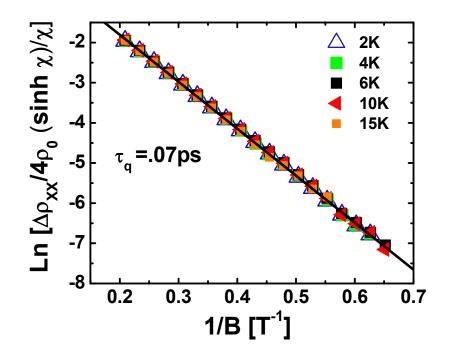

| Figure 4-25. Dingle plot used to extract quantum lifetime                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

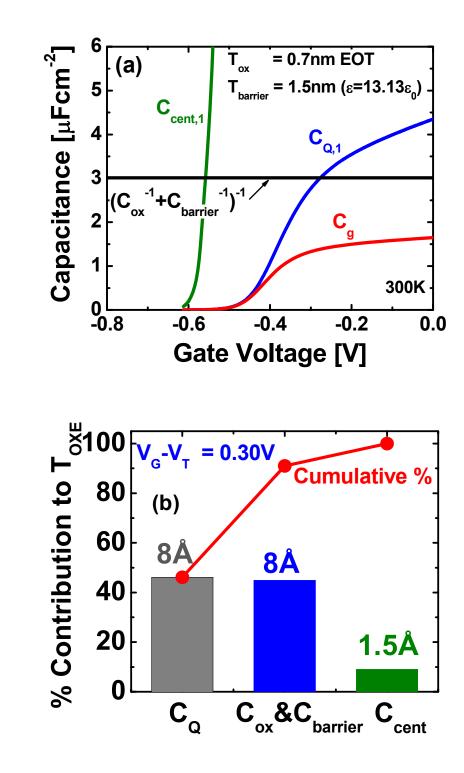

| Figure 4-26. (a) Components of the gate capacitance of $InAs_{0.8}Sb_{0.2}$ QW-MOSFET with a scaled dielectric and barrier, and (b) Percentage contribution of various components of gate capacitance to $1/C_g$                                                                                                                                                                                                                                                               |

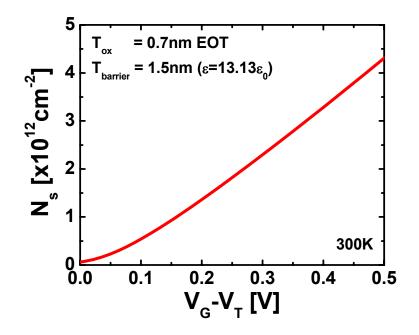

| Figure 4-27. Sheet charge density in the quantum well as a function of gate overdrive for InAs <sub>0.8</sub> Sb <sub>0.2</sub> QW-MOSFET with a scaled oxide and barrier. The threshold voltage is defined at the gate bias for which $N_s = 5 \times 10^{10} \text{ cm}^{-2}$                                                                                                                                                                                                |

| Figure 5-1. Electron and hole mobility of various III-V compound semiconductors [63].<br>Antimonides are very attractive since they have high electron as well as high hole<br>mobility                                                                                                                                                                                                                                                                                        |

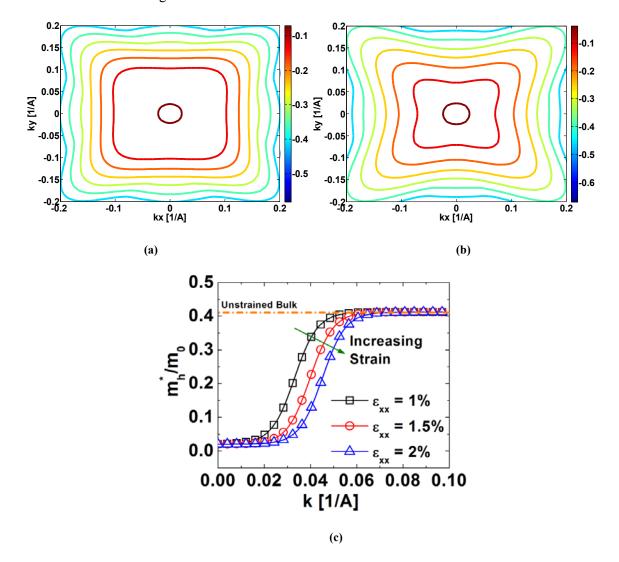

| <ul> <li>Figure 5-2. (a) Constant energy surfaces of the valence band of bulk InSb (unstrained)</li> <li>(b) Constant energy surfaces of the valence band of bulk InSb at 2% compressive strain (c) 6-band k.p simulation of in-plane effective hole mass as a function of energy for different compressive strain levels in InSb. For a given energy, higher compressive strain results in lower effective hole mass.</li> </ul>                                              |

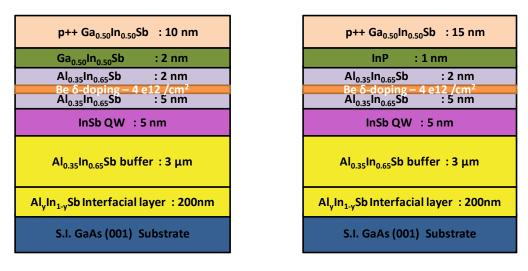

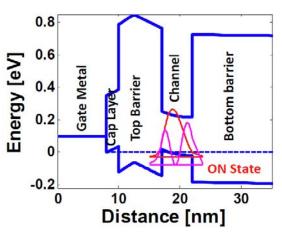

| Figure 5-3. <b>(a-b)</b> Schematic of the p-channel InSb quantum well heterostructure with $Ga_{0.5}In_{0.5}Sb$ or InP cap layer. The quantum well is 2% compressively strained. The $Ga_{0.5}In_{0.5}Sb$ or InP cap layer is used for obtaining a high quality interface with the high- $\kappa$ dielectric <b>(c)</b> Energy band diagram of the quantum well heterostructure under the gate (without the dielectric) showing good confinement of holes in the InSb channel. |

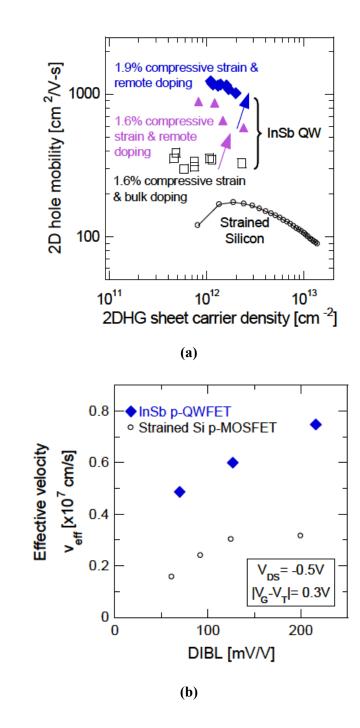

| Figure 5-4. (a) Hole mobility vs. sheet carrier density measurements for InSb QW showing mobility improvement with increasing compressive strain and remote doping. (b) Effective hole velocity (veff) vs. DIBL comparing InSb p-channel compressively strained QWFETs to strained Si p-channel MOSFETs at $V_{DS}$ = -0.5V and $ V_G-V_T $ =0.3V. (Source: Intel, IEDM 2008 [64])                                                                                             |

# LIST OF TABLES

| Table 4-1. Table comparing the capacitance components of Sb nMOSFET with the sc          | aled |

|------------------------------------------------------------------------------------------|------|

| gate stack and that of 40nm L <sub>G</sub> strained Si. The composite barrier of Sb nMOS | FET  |

| is same has the same EOT as that of the high-k/SiON gate stack of the straine            | d Si |

| MOSFET                                                                                   | 83   |

#### ACKNOWLEDGEMENTS

I owe my gratitude to all those people who have made this dissertation possible and because of whom my graduate experience has been one that I will cherish forever.

First, I would like to express my deepest sense of gratitude to my advisor, Dr. Suman Datta for giving me an opportunity to work in the exciting area of high performance logic transistors. His inspiration and guidance have motivated me throughout my dissertation work. The intellectual and personal growth that I have experienced under his supervision cannot be overstated. I express my gratitude to my collaborators Dr. Brian Bennett and Dr. Brad Boos for helping me with growth of antimonide quantum well device layers and Dr. Mantu Hudait for supplying GaSb wafers. I am also grateful to Gilbert Dewey, for the rewarding learning experience from his mentorship during my internship in the Novel Device and Dielectric Lab at Intel Corporation.

I would also like thank my committee members Dr. Suzanne Mohney, Dr. Jerzy Ruzyllo, Dr. Theresa Mayer, Dr. Vijay Narayanan and Dr. Peter Schiffer for reading previous drafts of this dissertation and providing many valuable comments that improved the presentation and contents of this dissertation. Special thanks to Dr. Suzanne Mohney and Dr. Peter Schiffer for helpful discussions during the course of my study and allowing me to use their labs for some experiments during my work. I like to acknowledge collaborations with Dr. Bob Wallace's group at UTD for X-ray Photoelectron Spectroscopy measurements, and Rajiv Misra in Peter Schiffer's group at Penn State for low temperature magnetotransport measurements. I would like to convey my special thanks and appreciation to the staff in the nanofabrication facility at Penn State, especially Kathy Gehoski, Chad Eichfeld, Guy Lavallee, Bangzhi Liu, and Yan Tang for for their help with training me at the Penn State Nanofab, as well as technical discussions on device fabrication during the course of my doctoral study.

I would also like to sincerely thank my colleagues Saurabh Mookerjea, Himanshu Madan, Dheeraj Mohata, Bijesh Rajamohanan, Euichul Hwang, Lu Liu, Ashish Agrawal, Nidhi Agrawal, Vinay Saripalli, Michael Barth and Feng Li for technical discussions. Special thanks to Himanshu Madan for his helps with S-parameter modeling of my devices. He also played a key role in the admittance modeling technique we co-developed at Penn State, an essential method in studying the quality of novel high-κ gate dielectrics for emerging semiconductors. I also thank Dr. Tom Jackson and Israel Ramirez for introducing me to the Plasma Enhanced Atomic Layer Deposition tool, which was used to deposit the high-κ gate dielectric for antimonide transistors.

I sincerely thank the Penn State Graduate School for selecting me for the Alumni Association Dissertation Award. I like to thank Suman once again for nominating me for this award, as well as the IBM PhD Fellowship Award. I like to acknowledge the financial support from SRC/DARPA supported MIT Materials, Structures and Devices Focus Center (MSD), and the 2011 IBM PhD Fellowship Award for my dissertation work.

Special thanks to my brother Afthaf Ali and my friends, Anoop Mohan, Anirudh Kondaveeti and Aravind Balan. Their support and care has helped me overcome setbacks and stay focused on my graduate study. I greatly value their friendship and deeply appreciate their belief in me. I like to thank my parents, Aliyaru Kunju and Suberath, who raised me very well with a strong sense of personal responsibility, courage and resilience, and prepared me for success in life. Their love, support and understanding has always motivated me to strive for excellence. Finally, and most importantly, I would like to thank my wife and best friend Anupa. Her encouragement, patience and unwavering love have certainly been the cornerstones on which the past few years of my life have been built. To my wife and parents, I dedicate this dissertation.

## Chapter 1

# Antimonide NMOSFET Device Design for Ultra-low Power Logic Applications

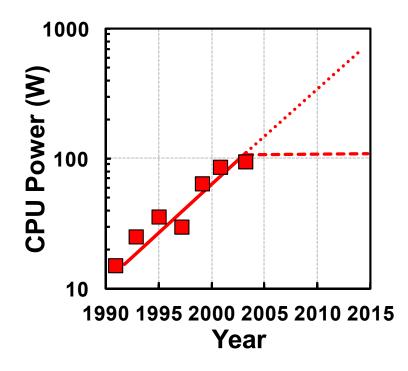

A transistor is essentially a "switch" which controls the flow of current between two terminals, using a "gate" that acts as a valve. The goal is to make this switch work at very high speed with very low power dissipation. Scaling the dimensions of transistors has led to exponential increase in density and switching speed, and a similar decrease in the switching energy [1]. The supply voltage of the transistor has been scaled in a similar proportion as the dimensions to reduce the power dissipation in the transistors as the number of transistors per chip increased exponentially. The processor power continued to rise even with scaling the supply voltage due to increased die size and fast frequency scaling [2]. As the total power dissipated in the microprocessor reached 100W (Figure 1-1), the frequency and die scaling were stopped. MOSFETs entered a "power constrained scaling" phase where the power dissipation was limited to 100W per chip [3]. To integrate more functions or to pack more transistors into the microprocessor, the supply voltage was required to be scaled. Since the threshold voltage and the sub-threshold slope of the transistor did not scale with the supply voltage [4], the leakage power density continued to increase as the supply voltage was scaled. Scaling the supply voltage without scaling the threshold voltage would lead to reduced switching speed and slower performance, which is not desired. Innovations in the past decade (high-k metal gate, strain and tri-gate architectures) have improved the performance of the transistors in the past decade and helped scale the supply voltage moderately (from  $\sim 1.2V$  for planar 65nm to  $\sim 0.9V$  for 22nm tri-gate transistors) [4].

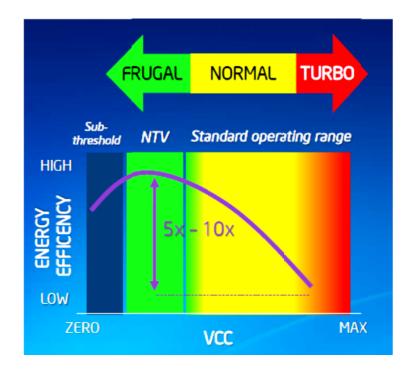

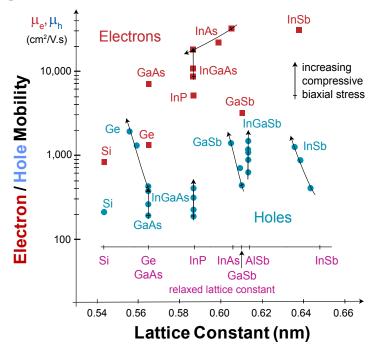

Future transistor scaling will require enhancement in device electrostatics (multigate), channel transport enhancement (beyond strained Silicon) and reduction in parasitics (contact, junction engineering etc.). Near threshold voltage operation can improve the energy efficiency of computing as shown in Figure 1-2, and can help scale the supply voltage [5]. Introducing a new material which has a higher carrier velocity than silicon would help to aggressively scale the supply voltage to around 0.5V, while maintaining the same or better performance levels as Si at high gate overdrive. III-V semiconductors comprising of elements from group III and V of the periodic table have extra-ordinary mobility (which translates to enhanced carrier velocities for short channel MOSFETs) compared to silicon and can help achieve near threshold voltage operation. Figure 1-3 shows the electron and hole mobility of various III-V compound semiconductors [1]. Antimonide based semiconductors are very attractive since they have high electron as well as high hole mobility.

Figure 1-1. Power dissipation in CPU for various technologies as a function of the year of introduction (Source: Intel [3])

Figure 1-2. Transistor operating voltage range showing energy efficient computation for near threshold voltage operation. (Source: Intel Labs ISSCC [5])

Figure 1-3. Electron and hole mobility of various III-V compound semiconductors (Source: del Alamo MIT [1]). Antimonides are very attractive since they have high electron as well as high hole mobility

#### I. Motivation: Unified Material System with High Electron and Hole Mobility

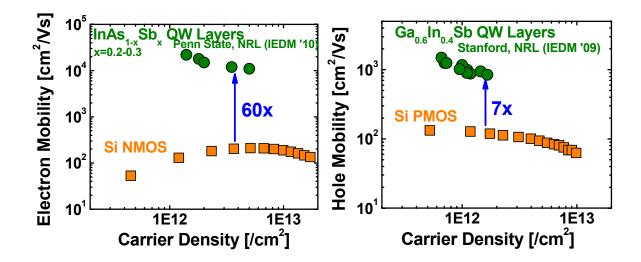

Due to their unique material properties, antimony (Sb) based III-V materials (materials comprised of elements from group III and V of periodic table) are of strong interest as channel material for low power all-antimonide complementary metal-oxide-semiconductor (CMOS) digital logic. Sb-based MOSFETs (Metal-Oxide-Semiconductor Field Effect Transistors) can operate at high speed and very low supply voltage, which promises to dramatically lower the power dissipation in future high-speed logic circuits. Antimonide based materials have high electron as well as high hole mobility [6][7]. Figure 1-4 shows the electron mobility of InAsSb QW heterostructure along with that of Si NMOSFET. For inversion carrier density of the order of  $3-4x10^{12}$ /cm<sup>2</sup>, InAsSb QW layers have a mobility of about ~ 13000 cm<sup>2</sup>/Vs, which is ~60x higher than that of Si NMOS inversion layers. This can give rise to a substantial improvement in drive current for InAsSb based devices which can help scale supply voltage to about 0.5V. Similarly if we compare the hole mobility of InGaSb quantum well heterostructure with that of Si PMOS, we see that for a hole density of about  $2x \ 10^{12}$ /cm<sup>2</sup>, the InGaSb QW layers have ~7x higher hole mobility compared to Si PMOS inversion layers.

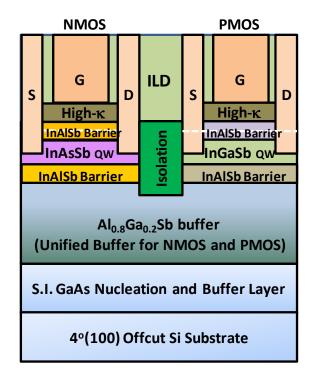

The antimonide NMOS and PMOS have similar lattice constants and they have a unified buffer which makes them very interesting. If we can integrate In AsSb QW NMOSFET and InGaSb QW MOSFET, we can envision a III-V complementary logic operating at low supply voltage. Figure 1-5 shows a schematic of Sb NMOS and PMOS integration for complementary logic operation.

Figure 1-4. Electron mobility of InAsSb QW heterostructure layers compared to that of Si NMOS inversion mobility and the hole mobility of InGaSb QW layers compared to that of Si PMOS inversion layers

Figure 1-5. Schematic showing integration of InAsSb NMOS and InGaSb PMOS for III-V complementary logic operation

#### II. Device Architecture of Sb QW MOSFET for Ultra-low V<sub>DD</sub> Logic

Figure 1-6. TEM micrographs of the  $InAs_{0.8}Sb_{0.2}$  QWFET stack grown on GaAs by MBE and the defect free active device layers

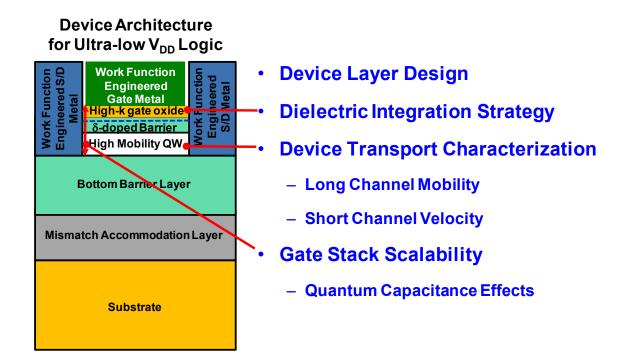

Figure 1-6 shows a schematic of the quantum well MOSFET device architecture for ultra-low supply voltage operation. The high mobility quantum well is confined within an insulating barrier layer. The quantum well is remote doped using a delta-doping layer in the barrier to provide low resistance access regions for source drain contact. The device has a high quality high-k dielectric integrated on top of the barrier layer to reduce gate leakage, and a work function engineered gate metal to target threshold voltage.

In this dissertation, I address the feasibility of Arsenide-Antimonide channel materials to enable high-performance low-power logic computing. There are three main challenges which are key to demonstrating high performance transistors operating at low supply voltage, -(1) A good quality interface between the channel material and the gate oxide, which determines the standby power dissipation in the device, (2) High drive current (current passed by the device when it is switched ON) which determines the switching speed of the device, and (3) Enhancement mode operation (device conducts only with the application of a gate voltage and is otherwise OFF), which is required for CMOS logic circuits.

This dissertation is organized as follows. In this chapter I, I will discuss about the device layer design for Sb NMOSFETs followed by the strategy for integrating a good quality high-k dielectric in chapter II. Device fabrication and characterization details are explained in chapter III. Chapter III concludes with benchmarking the device figures of merit of the Sb NMOS, particularly the long channel mobility and short channel effective velocity, with that of the standard strained silicon NMOS. Enhancement mode device characteristics are presented in chapter III. In chapter IV, I will discuss the quantum capacitance and band non parabolicity measurements and address the effects of quantum capacitance on gate stack scalability and performance of these devices. I will conclude this dissertation with the future works section in Chapter V. My research works show that antimonide transistors are really promising for highperformance low-power logic applications, if the key issues on gate stack quality and external resistance are addressed. For these devices to compete with the state-of-the-art Silicon tri-gate devices, the device architecture has to evolve from a planar to three-dimensional fashion, or a gate wrap-around structure

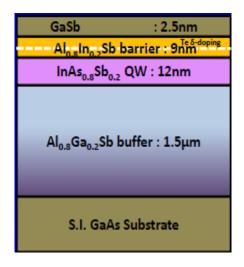

### III. Device Layer Design and Characterization

The device layer design for InAsSb quantum well MOSFET is shown in Figure 1-7. The device is metamorphically grown on GaAs since there is no lattice matched substrate for InAsSb. The quantum well is undoped and the  $Al_{0.9}ln_{0.1}Sb$  barrier layer has been delta-doped with Te to provide carriers to the access regions. The device layers are grown by Dr. Brian Bennett at Naval

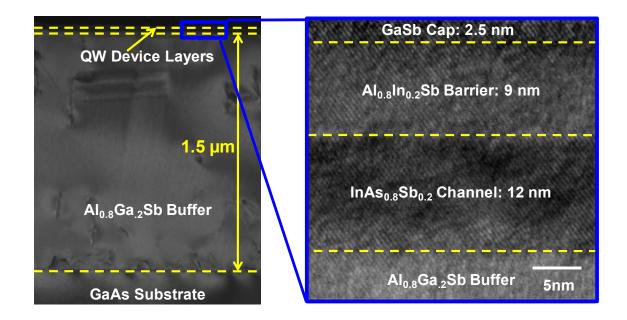

Research Lab, Washington DC. Figure 1-8 shows the TEM micrographs of the  $InAs_{0.8}Sb_{0.2}$ QWFET stack grown on GaAs by MBE and the defect free active device layers There is ~9% lattice mismatch between the channel and the GaAsb substrate, which is accommodated as defects in the bottom buffer layer as seen from the cross-section TEM picture.

Figure 1-7. Schematic of the Sb QW MOSFET device layers

Figure 1-8. TEM micrographs of the  $InAs_{0.8}Sb_{0.2}$  QWFET stack grown on GaAs by MBE and the defect free active device layers

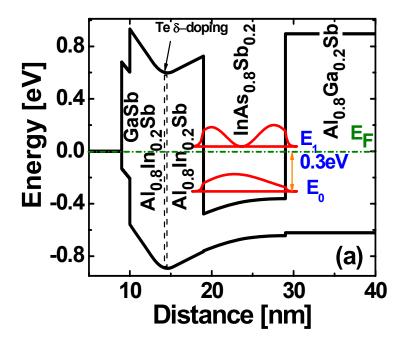

The InAlSb barrier layer can have oxidation problems while depositing high-k dielectric. So I have introduced a thin layer of GaSb on the top to make a good interface with the dielectric. Incorporation of GaSb layer is a key difference that separates the Sb MOSFET structure from the previous HEMT works on antimonide systems [7]. The energy band diagram of the device in Figure 1-9 shows that the carriers are efficiently confined within the quantum well and that there is no carrier spill over to the barrier.

Figure 1-9. Energy band diagram of the InAsSb QWFET device layers showing carriers confined effectively in the QW with no carrier spill over to the barrier layer

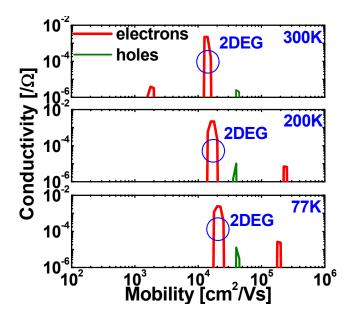

As this structure is metamorphically grown on GaAs, it is important to see if there is any parallel conduction in the device layers due to defects at the material interface. So I studied the quantitative mobility spectrum analysis [8] of this device as a function of temperature to identify if the transport it confined to the Sb QW itself. In QMSA, the conductivity tensor of a Hall device is studied as a function of magnetic field. The sheet resistance and the hall resistance obtained from Hall measurements are converted to the conductivity tensor. By numerically solving the

conductivity tensor as a function of magnetic field, we can identify if there is multi-carrier transport in the device. Figure 1-10 shows the quantitative mobility spectrum analysis (QMSA) for the QW heterostructure obtained using magneto conductance measurements at various temperatures and under varying magnetic field. There is a large conductivity ratio between the majority carrier (electrons) and the minority carrier (holes) at all temperatures. The single dominant conductivity peak due to electrons indicates that there is no parasitic or parallel conduction through the barrier or the metamorphic buffer layers.

Figure 1-10. Quantitative mobility spectrum analysis (QMSA) for the QW heterostructure obtained using magneto-conductance measurements at various temperatures and under varying magnetic field

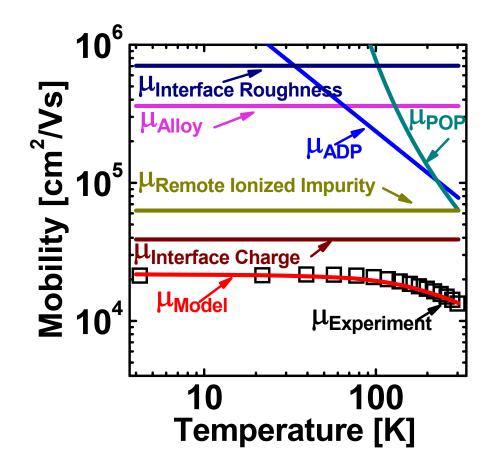

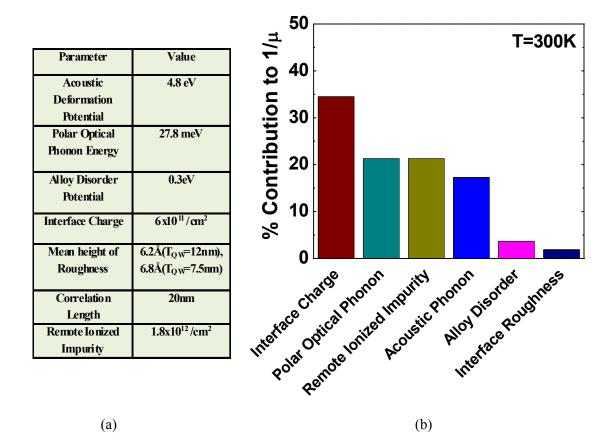

The as grown device layers exhibit an electron mobility of  $13,000 \text{ cm}^2/\text{Vs}$  at 300K at carrier density of  $2.2 \times 10^{12} / \text{cm}^2$ . Figure 1-11 shows the measured and modeled Hall mobility as a function of temperature. The Hall mobility was modeled using various scattering mechanisms including acoustic deformation potential scattering, polar optical phonon scattering, remote ionized impurity scattering, alloy disorder scattering, interface roughness scattering, and coulomb scattering due to charge trapped at the barrier and channel interface. As can be seen from the

temperature dependence of the Hall mobility, the low temperature mobility is limited by interface charge scattering. This charge could be at the hetero interface of the InAlSb and InAsSb layers due to Tamm States arising from AlAs and InSb phase formation while growing an abrupt interface between the QW and barrier layer [9]. Figure 1-12 (a) shows the various parameters used in the modeling of scattering mechanisms, and Figure 1-12 (b) shows the percentage contribution of various scattering mechanisms toward  $1/\mu$  at room temperature. Coulomb scattering due to interface limits the electron mobility at room temperature.

Figure 1-11. Hall mobility of the Sb QW device layer as a function of temperature from 4K-300K

Figure 1-12. (a) Parameters used for modeling the different scattering mechanisms (b) Percentage contribution of different scattering mechanisms to the  $1/\mu$  at room temperature showing the mobility is limited by Coulomb scattering due to interface charge

In summary, the Sb quantum well device layers have very high mobility and no parallel conduction, suitable for fabricating MOSFETs. A good quality dielectric is required to be integrated on these device layers to scale the device, which is discussed in the next chapter.

## Chapter 2

## **Dielectric Integration Strategy**

#### I. Introduction

Integrating a high quality dielectric is key to demonstrating a scalable antimonide (Sb) quantum well (QW) MOSFET architecture for high performance low-power logic applications. The Sb QW MOSFET has  $Al_vIn_{1-v}Sb$  as the barrier layer which is highly reactive. This has been one of the major obstacles in the development of antimonide based FETs. The aluminum containing barrier layer oxidizes very rapidly on exposure to air. The Al<sub>v</sub>In<sub>1-v</sub>Sb material increases in volume on oxidizing which would then lead to cracking and further oxidation of the entire epitaxial layer [10]. This oxidation of  $Al_v In_{1,v}Sb$  was observed by many researchers who worked on InAs-AlSb HEMTs [11][12][13]. Further the oxidation of InAlSb would leave behind oxides of aluminum (Al) and antimony (Sb), as well as metallic antimony at the surface. On forming an MOS (metal-oxide-semiconductor) gate stack on the Al<sub>v</sub>In<sub>1-v</sub>Sb barrier layer for making the Sb MOSFET, the native oxides (of Al and Sb) and the metallic Sb species would give rise to interface traps, which then screen the gate potential from modulating the channel potential. If this happens, the charge in the Sb QW channel (or the Fermi level in the channel) cannot be modulated with the gate potential and this is called Fermi level pinning. I found out experimentally that an ultra-thin GaSb surface layer which caps the InAlSb barrier layer is more favorable toward high- $\kappa$  dielectric integration than Al<sub>v</sub>In<sub>1-v</sub>Sb top barrier layer for the Sb MOSFET, as it avoids Al at the interface and the associated surface oxidation. Figure 2-1 shows the effect of surface passivation treatment with HCl (surface treatment prior to dielectric integration) on the Sb QW samples with and without the GaSb cap. The sample without GaSb cap

where the InAlSb surface was exposed to HCl showed pits uniformly throughout the sample due to oxidation of InAlSb, whereas the sample with the GaSb cap layer exhibited a smooth surface after HCl treatment. In this chapter, the electrical characteristics of high-k/GaSb semiconductor interface are carefully examined to evaluate its potential to be integrated on the Sb MOSFET.

Figure 2-1. Optical micrograph of device layers after HCl surface treatment step on, (a) sample without GaSb cap (top InAlSb barrier layer is exposed to HCl), and (b) sample with GaSb cap

GaSb has a highly reactive surface and on exposure to air it will form a native oxide layer composed of Ga<sub>2</sub>O<sub>3</sub> and Sb<sub>2</sub>O<sub>3</sub> (2GaSb +  $3O_2 \rightarrow Ga_2O_3 + Sb_2O_3$ ). The Sb<sub>2</sub>O<sub>3</sub> can further react with the GaSb surface forming elemental Sb and Ga<sub>2</sub>O<sub>3</sub> (Sb<sub>2</sub>O<sub>3</sub> + 2GaSb  $\rightarrow$  Ga<sub>2</sub>O<sub>3</sub> + 4Sb) [14][15]. Chemical treatments based on HCl are effective in removing native oxides on GaSb [15][16]. I studied the effects of HCl treatment on the capacitancevoltage characteristics (C-V) and the surface chemistry of n-type and p-type GaSb (100) MOS capacitors with Al<sub>2</sub>O<sub>3</sub> dielectric fabricated using both Atomic Layer Deposition (ALD) and Plasma Enhanced ALD (PEALD) techniques. PEALD was employed to reduce the thermal budget of dielectric deposition, particularly important for antimonide based semiconductors. In this chapter, I demonstrate an unpinned Fermi level in GaSb MOS system with a high- $\kappa$  PEALD Al<sub>2</sub>O<sub>3</sub> dielectric, using temperature resolved admittance spectroscopy and monochromatic X-ray photoelectron spectroscopy (XPS) analysis.

## II. GaSb MOS Capacitor Fabrication

#### ALD vs Plasma Enhanced ALD

Atomic layer deposition (ALD) has widely been used to form high quality dielectrics for the gate stack of MOS transistors. In the ALD process, the substrate is exposed to a metal organic compound for a certain period of time. The metal organic adsorbs to the surface of the substrate uniformly. This step is followed by an inert gas purge step which will evacuate the chamber of any unreacted precursor. A second precursor or reactant is now purged for a short period of time which then reacts with the adsorbed metal organic species on the surface forming a high quality conformal thin film on the surface. To form a high quality thin film during the reaction between the metal organic and the reactant, the temperature of the substrate is kept high. Typically higher temperatures are preferred for film growth. However very high temperatures would lead to desorption of the metal organic species already adsorbed on to the substrate. A suitable temperature of growth is preferred which gives rise to a good quality dense film while maintaining a conformal coating of metal organic.

In the case of antimonide semiconductors, it is desired to reduce the temperature of dielectric deposition to prevent the oxidation of GaSb to  $Ga_2O_3$  and metallic Sb [16]. Figure 2-2 shows compares the conventional ALD process with a new Plasma Enhanced ALD (PEALD) process in which the inert gas purge is replaced with a weak oxidant gas like  $CO_2$ , which acts as the oxidant when the plasma is pulsed. Since the reaction is plasma assisted it helps to lower the

deposition temperature. More details on the PEALD process can be obtained in [17]. A schematic representation of the sequence of steps in the ALD and PEALD processes is shown in Figure 2-3.

Figure 2-2. Schematic of (a) conventional ALD process with a strong reactant, and (b) Weak oxidant PEALD process with a pulsed plasma sequence to form the oxide

### III. Results and Discussion

#### C-V/G-V Characterization of GaSb MOS Capacitors

Both n-type and p-type GaSb (100) MOS capacitors were fabricated with high- $\kappa$  Al<sub>2</sub>O<sub>3</sub> gate dielectric. The samples were degreased in acetone and ethanol for 5 min each and rinsed in isopropyl alcohol (IPA). The degrease step was followed by a dip in concentrated HCl (HCl :  $H_2O = 1:2$ ) for 5 min to remove surface oxides followed by an IPA rinse. GaSb MOS capacitors were fabricated with Al<sub>2</sub>O<sub>3</sub> deposited by ALD at 300°C from trimethylaluminum (TMA) and water or by PEALD at 200°C from TMA and CO<sub>2</sub>. Pt/Au gate metallization was done using electron beam evaporation after defining gate patterns using optical lithography. Pd/Au backside

Figure 2-3. Schematic illustration of the thin film deposition process using ALD and PEALD (Source: Cambridge Nanotech Corporate Brochure June 2010.)

ohmic contacts were deposited using electron beam evaporation. No post deposition anneal was done for any of the samples.

Capacitance voltage (C-V) and conductance voltage (G-V) measurements were obtained with HP 4285A precision LCR meter. Figure 2-4 shows the C-V measurements on ALD Al<sub>2</sub>O<sub>3</sub>/n-GaSb and PEALD Al<sub>2</sub>O<sub>3</sub>/n-GaSb MOS capacitors. The ALD sample shows weakly pinned C-V characteristics with very fast interface trap density  $(D_{ii})$  response whereas PEALD sample demonstrates good Fermi level modulation. The accumulation side of C-V characteristics for the PEALD sample shows the effect of high  $D_{it}$  near conduction band and the negative bias regime shows the effect of inversion response along with a low  $D_{it}$  response. The accumulation side of the admittance data is analyzed using the standard depletion/accumulation model [18] and the inversion side using the model introduced in [19]. The circuit model in inversion accounts for the supply of minority carriers through bulk thermal generation and diffusion across the space charge layer along with interface state contribution, which enables accurate modeling of the admittance data in inversion. Figure 2-5 shows C-V characteristics of the ALD Al<sub>2</sub>O<sub>3</sub>/p-GaSb and PEALD  $Al_2O_3/p$ -GaSb samples with HCl treatment for different temperature. The ALD sample shows strongly pinned C-V characteristics with both accumulation and inversion regimes completely dominated by interface states. For the PEALD sample, there is minimal dispersion of capacitance in accumulation due to less  $D_{it}$  near the valence band whereas the inversion response shows contributions from minority carriers as well as high  $D_{it}$  near the conduction band. The 200K C-V shows a clear Fermi level movement from accumulation to depletion for the PEALD sample whereas ALD sample exhibits pinned C-V characteristics.

*C-V* measurements for the n-type (p-type) MOS capacitors were done at 300K and 250K (300K and 200K). The reason is that the backside contact (Pd/Au) on GaSb is ohmic for holes whereas it forms a Schottky barrier for electrons ( $\sim 0.6$  eV Schottky barrier height for electrons due to the Fermi stabilization energy in GaSb being  $\sim 0.1$ eV from valence band as mentioned in

[20]. This Schottky barrier gives rise to higher contact resistance for electrons at lower temperatures, which causes frequency dispersion in the accumulation capacitance of the n-type MOSCAPS.

Figure 2-4. *C-V* characteristics as a function of frequency of n-type ALD and PEALD MOS capacitors with HCl treatment. Measurement temperature is indicated in the figure.

For the p-type devices this is not a problem as the contacts are ohmic for holes, and the measurement can be done at very low temperature. Hence, to avoid parasitic series resistance in the measurement, the above measurement temperatures were employed

Figure 2-5. *C-V* characteristics as a function of frequency of p-type ALD and PEALD samples with HCl treatment. Measurement temperature is indicated in the figure.

Figure 2-6 shows the conductance contour map  $(G/\omega)$  of n-type and p-type PEALD samples as a function of gate voltage and small-signal frequency. The V-shaped trajectory of the peak value of conductance,  $(G/\omega)_{peak}$ , along the frequency axis shows that the Fermi level moves freely on either side of the midgap of GaSb. PEALD Al<sub>2</sub>O<sub>3</sub>/GaSb samples demonstrate an unpinned Fermi level at the interface, even though the Fermi stabilization energy for GaSb is 0.1eV from valence band [20].

Figure 2-6. Conductance  $(G/\omega)$  contours of n-type and p-type GaSb MOSCAPs with PEALD Al<sub>2</sub>O<sub>3</sub> showing good Fermi level modulation towards valence and conduction band sides.

The extracted capture cross section values are  $9 \times 10^{-15}$  cm<sup>2</sup> for traps near valence band and  $8 \times 10^{-19}$  cm<sup>2</sup> for traps near conduction band, indicating that the traps near the valence band are faster than those near the conduction band. Hence, the conductance plots were done at lower temperature for the p-type samples where the conductance peaks were visible. The capture cross section values are consistent with [21], where irradiated p-type GaSb showed acceptor type traps near the valence band with higher capture cross-section.

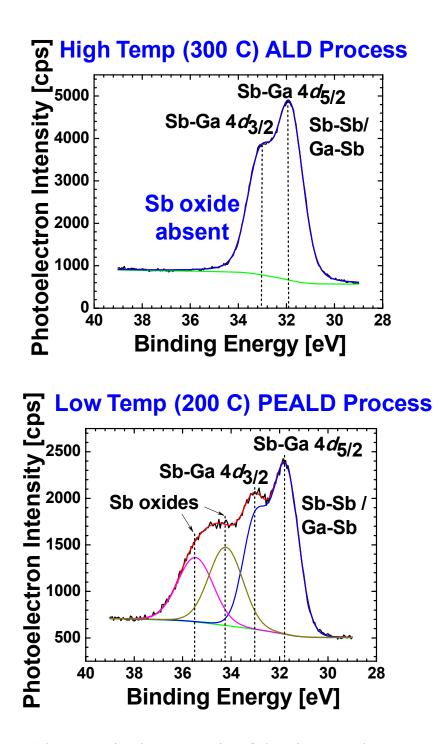

#### Interface Chemical Analysis with X-ray Photoelectron Spectroscopy (XPS)

Figure 2-7 shows the monochromatic XPS analysis of the Sb 4*d* region for the ALD and PEALD samples with HCl treatment. XPS measurements were done in collaboration with Dr. Bob Wallace's group at UTD and more details on the XPS measurement system can be found in [22]. All PEALD and ALD samples show presence of Ga-oxides. The ALD samples show no detectable Sb-oxides where as the PEALD samples have significant Sb-oxides. As mentioned before, Sb<sub>2</sub>O<sub>3</sub> reacts with GaSb forming Ga<sub>2</sub>O<sub>3</sub> and elemental Sb: Sb<sub>2</sub>O<sub>3</sub> + 2GaSb  $\rightarrow$  Ga<sub>2</sub>O<sub>3</sub> + 4Sb [15]. The kinetics of this reaction is enhanced at higher temperatures>200°C [23]. Enhanced thermal desorption of Sb-oxides are also anticipated at such temperatures [24]. The ALD, which was done at 300°C, could therefore result in significant formation of elemental Sb, thereby reducing the available Sb<sub>2</sub>O<sub>3</sub>. In contrast, the PEALD was done at 200°C where the reduction is significantly suppressed. The 4*d* orbital binding energy of elemental Sb (Sb-Sb) is similar to that for GaSb. Hence, due to the Al<sub>2</sub>O<sub>3</sub> thickness, it is difficult to conclude whether the PEALD samples are free from elemental Sb. It is possible that the Fermi level, E<sub>F</sub>, unpinning for PEALD samples is due to the absence of elemental Sb at the Al<sub>2</sub>O<sub>3</sub>/GaSb interface. Further, the absence of water in PEALD, coupled with low thermal budget, leads to a better quality interface.

Figure 2-7. XPS data comparing the concentration of  $Sb_2O_3$  in ALD and PEALD samples. Reduction of  $Sb_2O_3$  in the (higher temperature) ALD samples is evident.

Finally, F was detected in all samples by XPS and is attributed to reactor O-ring decomposition. The role of F remains a topic of investigation.

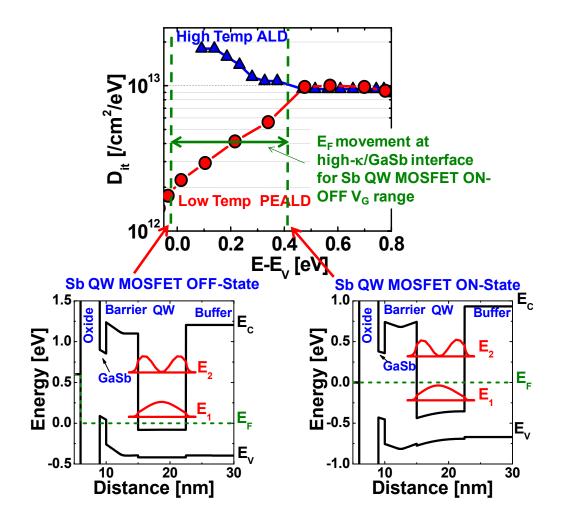

#### Fermi Level Unpinning of GaSb MOS Capacitors

Figure 2-8 shows the  $D_{it}$  extracted from multi-temperature C-V / G-V analysis of the ntype and p-type GaSb MOSCAPs using the admittance modeling technique mentioned in [18]. Band diagrams showing the positions of Fermi level at the GaSb interface for the range of operation of the Sb QW MOSFET is also shown in Figure 2-8. For the range of operation of the Sb QW MOSFET, the Fermi level at the GaSb interface sweeps from the valence band towards midgap where the  $D_{it}$  is relatively low.

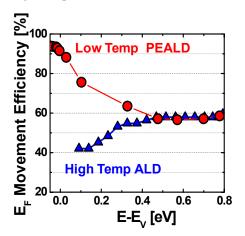

Figure 2-9 shows the Fermi level movement efficiency of the ALD and PEALD samples. Fermi level movement efficiency is defined as the ratio of the change in the Fermi level at the oxide-semiconductor interface in the presence of  $D_{ii}$  to the change in Fermi level without  $D_{it}$ , for a unit applied gate voltage. Mathematically, it can be represented as:

$$E_{\rm F} \text{ movement efficiency} = \frac{(\delta \psi_s / \delta V_g) \text{with } D_{it}}{(\delta \psi_s / \delta V_g) \text{ideal}} \% = \frac{1 + C_{dep} / C_{ox}}{1 + (C_{dep} + C_{it}) / C_{ox}} \%$$

(1)

The PEALD sample with HCl pretreatment shows a 90%  $E_F$  movement efficiency near the valence band. This makes it suitable for integration with Sb QW MOSFET, where the Fermi level sweeps near the valence band of GaSb.

Figure 2-8. Extracted  $D_{it}$  from multi-temperature C-V/G-V analysis of n and p type GaSb MOSCAPs showing low  $D_{it}$  near  $E_V$  for PEALD Al<sub>2</sub>O<sub>3</sub>/GaSb interface. Fermi level movement at the GaSb interface for the range of operation of the Sb QW MOSFET is also shown.

Figure 2-9. Fermi level movement efficiency of GaSb MOSCAPs with ALD and PEALD Al<sub>2</sub>O<sub>3</sub>

I have also studied the *C-V* characteristics of GaSb samples with ALD Al<sub>2</sub>O<sub>3</sub> deposited at a lower temperature (250°C). A bilayer oxide stack with 1nm Al<sub>2</sub>O<sub>3</sub> and 5.5nm HfO<sub>2</sub> was investigated. The bilayer stack was introduced to enable gate stack scaling. The *C-V* characteristics as shown in Figure 2-10 exhibited much better gate modulation (i.e. higher  $C_{max}/C_{min}$  ratio) compared to the 300°C ALD sample, and is comparable to the *C-V* characteristics of the low temperature PEALD Al<sub>2</sub>O<sub>3</sub> process (200 °C). This is due to the reduced amount of elemental Sb formation at 250°C. The  $D_{ii}$  extracted from multi-temperature *C-V/G-V* analysis is shown in Figure 2-11. The 250°C ALD sample has comparable  $D_{ii}$  profile as the 200°C PEALD process, but has slightly higher  $D_{ii}$  than the PEALD process. I also speculate that the oxide anions in the plasma during the PEALD process may more efficiently oxidize the elemental Sb back to Sb<sub>2</sub>O<sub>3</sub>. I have investigated lower temperature ALD process (Al<sub>2</sub>O<sub>3</sub> at 200°C), which exhibited unpinned *C-V* characteristics (not shown here) similar to the ALD 250°C process, however the gate leakage currents in those devices where higher. This could be due to non-uniform nucleation of the metal organic during the ALD growth process.

Figure 2-10. *C-V* of n and p type GaSb MOS capacitors with 1nm Al<sub>2</sub>O<sub>3</sub> - 5.5 nm HfO<sub>2</sub> dielectric stack deposited using low temperature (250 C) ALD process

Figure 2-11. Extracted  $D_{it}$  from multi-temperature C-V/G-V analysis of n-type and p-type GaSb MOSCAPs showing low  $D_{it}$  near valence band for both low temperature ALD and low temperature PEALD process.

#### Band Alignment of GaSb with Al<sub>2</sub>O<sub>3</sub>

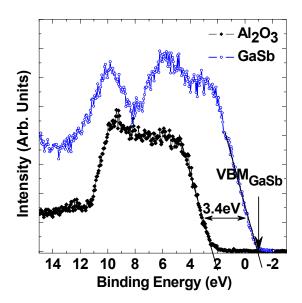

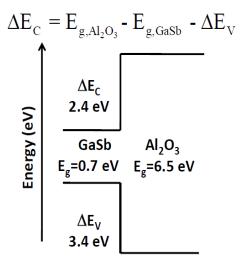

XPS measurements were used to determine the conduction and valence band offsets of Al<sub>2</sub>O<sub>3</sub> with GaSb. These measurements were done in collaboration with Mozhe Eiseberg's group at Technion Institute, and are mentioned in detail in [25]. The bandgap of Al<sub>2</sub>O<sub>3</sub> was first determined from the O 1s core level spectrum. The energy loss of O 1s photoelectrons for thick 20 nm Al<sub>2</sub>O<sub>3</sub> film is shown in Figure 2-12. The energy loss region is shown in the inset where the difference between the middle of the peak and the beginning of the energy loss region (shown in inset of Figure 2-12) gives the bandgap energy. The obtained energy bandgap value is 6.5 eV which is consistent with literature. The valence band offset of Al<sub>2</sub>O<sub>3</sub> relative to GaSb is obtained from the difference in energy between the valence band spectra of Al<sub>2</sub>O<sub>3</sub> and GaSb as shown in Figure 2-13. The obtained valence band offset is 3.4 eV±0.2 eV. The conduction band offset is now calculated from the band alignment noting that  $\Delta E_C + \Delta E_C + E_{g,GaSb} = Eg$ , AlO<sub>3</sub>. The obtained

$\Delta E_C$  was 2.4±0.1 eV. A schematic of the band alignment of Al<sub>2</sub>O<sub>3</sub> with GaSb is shown in Figure 2-14.

Figure 2-12. O 1s energy-loss spectrum for 20 nm  $Al_2O_3$  film. The inset is a magnified region of the energy loss spectrum.

Figure 2-13. Valence band spectra of Al<sub>2</sub>O<sub>3</sub> and GaSb (More details of the band offset determination procedure is reported in [25].

Figure 2-14. Schematic band alignment of Al<sub>2</sub>O<sub>3</sub> with GaSb

$GaSb/A_2O_3$  interface has a symmetric conduction and valence band alignment reduces both electron and hole leakage. Figure 2-15 shows the leakage current density as a function of gate voltage for GaSb MOS capacitors with  $Al_2O_3$ , which gives very low gate leakage for all ranges of applied bias.

Figure 2-15. Gate leakage of GaSb MOS capacitors with Al<sub>2</sub>O<sub>3</sub>

# IV. Conclusions

In summary, I have demonstrated GaSb MOS capacitors (p-type and n-type) with unpinned Fermi level using PEALD  $Al_2O_3$  by minimizing elemental Sb at the GaSb/Al\_2O\_3 interface. The reduction of Sb<sub>2</sub>O<sub>3</sub> to metallic Sb is suppressed with PEALD due to lower deposition temperature, which is confirmed by XPS analysis. The  $D_{ii}$  is low near the valence band which makes GaSb-PEALD  $Al_2O_3$  a good interface for composite barrier design with  $Al_yIn_{1-y}Sb$ and  $Al_yGa_{1-y}Sb$  barrier layers in mixed-anion QW MOSFETs for ultra-low power logic applications. Further, the GaSb/Al<sub>2</sub>O<sub>3</sub> interface has a symmetric band alignment which reduces both electron and hole leakage.

# Chapter 3

### Antimonide MOSFET Fabrication and Characterization

# I. Introduction