## Extraction of Near Interface Trap Density in Top Gated Graphene Transistor Using High Frequency Current Voltage Characteristics.

Himanshu Madan<sup>1</sup>, Matthew J. Hollander<sup>1</sup>, Joshua A. Robinson<sup>2</sup>, and Suman Datta<sup>1</sup> <sup>1</sup>Electrical Engineering, The Pennsylvania State University, University Park, PA 16802, USA <sup>2</sup>Material Science and Engineering. The Pennsylvania State University, University Park, PA 16802, USA Phone: (304) 216 5493, Fax: (814) 865 7065, E-mail: himanshu@psu.edu

Graphene as a material has created a lot of interest due to properties like high saturation velocity [1], high current carrying capacity, ambipolar characteristics [2] and high transconductance. These properties make graphene based transistors a promising candidate for high frequency applications. Recently, there have been [2-3] demonstration of RF mixers with graphene transistors. Traditional DC measurements are not sufficient when considering graphene transistors for high frequency circuit design, making it essential to study the transistor IV performance at operating frequencies >GHz. In this work we outline an RF IV extraction technique and use physics based analytical model to evaluate the performance of graphene transistors with HfO<sub>2</sub> high- $\kappa$  dielectric.

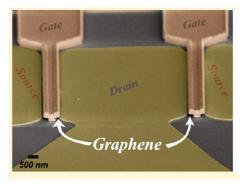

Figure 1 shows an SEM micrograph of the fabricated transistor on quasi-free-standing graphene (QFEG). QFEG is prepared on (0001) oriented 6H-SiC substrates through a combination of sublimation and hydrogen intercalation [4]. The sublimation of Si takes place at  $1625^{\circ}$ C for 15 minutes under a 1 Torr Ar ambient, while hydrogen intercalation follows at  $1050^{\circ}$ C for 120 minutes in a 600 Torr Ar/H<sub>2</sub> mixture, producing monolayer and bilayer QFEG. Ti (10 nm)/Au (100 nm) contacts are used as source/drain metallizations, after which gates are prepared. HfO<sub>2</sub> dielectric (10 nm thick) was deposited using an oxide seeded ALD (O-ALD) technique previously described in detail elsewhere [5].

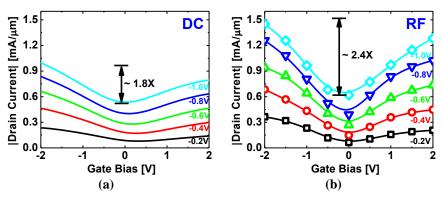

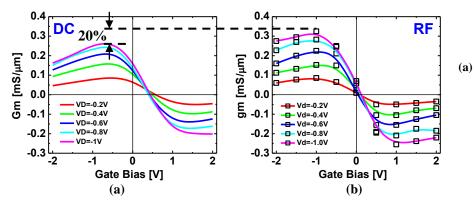

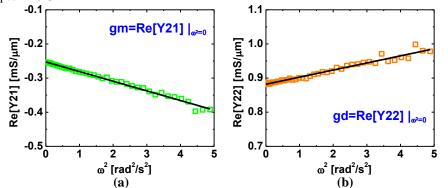

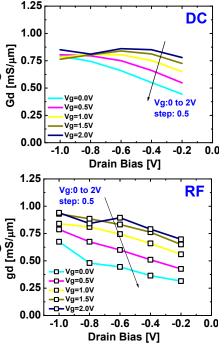

The DC transfer characteristics of a 750nm gate length device are shown in Figure 2a. Figure 3a and 4a shows the DC transconductance (*Gm*) and output conductance (*Gd*) of the measured device. For the evaluation of RF IV (fig. 2b) it is essential to first evaluate the non-linear components (*gm*, *gd*) of the small signal model representing the device at high frequency. The s-parameters for the device are measured at the desired gate and drain bias conditions. After open and short de-embedding, the s-parameters are converted into y-parameters. Figure 5 shows the real part of Y<sub>21</sub> and Y<sub>22</sub> de-embedded data as a function of angular frequency ( $\omega$ ). The Y-intercept of these curves provides us with the RF *gm* and *gd*. Figure 3b and 4b shows the extracted RF *gm* and *gd* as a function of gate and drain bias. Through the integration of the evaluated *gm* and *gd* over gate and drain bias respectively, the RF current-voltage characteristics of the graphene FET is evaluated.

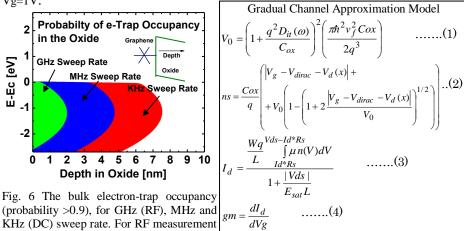

The RF source to drain current,  $i_{on}$  improves by 50% and the peak RF gm improves by 20% compared to DC  $I_{on}$  and Gm. This improvement is due to reduced charge trapping in the dielectric at very high frequencies. The two primary sources of traps in transistors are interface traps and bulk dielectric traps. The trap response time of interface traps is exponentially related to the energetic distance from the band edges. For example, midgap traps are the slowest while band edge traps are the fastest. In graphene, due to the absence of a bandgap these traps can readily exchange carriers with either the valance or the conduction band. Hence, even at RF measurement frequencies, these traps are active and degrade the RF IV characteristics. Alternatively, the bulk traps in the dielectric are slow traps as they rely on tunneling of the carriers into the oxide. Figure 6 shows the occupancy (probability>0.9) of bulk electron traps extending into the dielectric for different sweep rate, by the capture of electron from the graphene conduction band. It can be seen that for RF measurement, only the traps  $1\sim 2$  nm deep will be active.

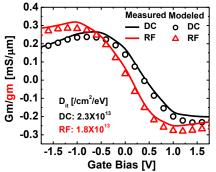

The measured RF and DC transconductance was modeled (Fig. 7) using the gradual channel approximation [Eq 3-4]. The model includes the effect of effective trap density ( $D_{it}$ ) [Eq1-2] [6], contact resistance and access resistance [Eq-3]. The series resistance for this device is 340 ohm-µm. The extracted effective  $D_{it}$ ,  $2.3x10^{13}$ /cm<sup>2</sup>/eV (DC) and  $1.8x10^{13}$ /cm<sup>2</sup>/eV (RF), shows the reduction in active traps at RF frequency confirming that the improvement in the RF IV performance is attributed to inactive slow bulk traps.

In summary, we have demonstrated for the first time the RF IV modeling of graphene transistors with  $HfO_2$  high- $\kappa$  dielectric. The extracted RF IV shows a 50% increase in current as compared to equivalent DC IV characteristics. The increase in current and transconductance is attributed to the reduction of active bulk traps at GHz frequency.

References

<sup>[1]</sup> A. Akturk, et al, J. App. Phys. 2008, 103, 053702. [2] H. Wang, et al, IEEE Electron Device Lett. 2010, 31, 9, 906–908.

<sup>[3]</sup> L. Yu-Ming, et al, Science, 2011, 332, 6035, 1294-1297. [4] J. A. Robinson, et al, Appl Phys Lett. 2011, 98, 053103.

<sup>[5]</sup> M. J. Hollander, et al, Nano Lett. 2011, 11, 3601-3607. [6] G. I. Zebrev, et al, Condens. Matter: Mesoscale Nanoscale Phys. 2010.

Fig. 1 SEM of fabricated graphene transistor in GSG configuration, with 10nm HfO<sub>2</sub> high-κ dielectric.

Fig. 2 (a) DC and (b) RF transfer characteristics of a 750nm gate length graphene FET. The drain bias is swept from -0.2V to -1.0V with a step size of 0.2. For the RF IV there is 1.5X increase in the drain current and 1.4X increase in the on to off ration as compared to DC IV measurement.

Fig. 3 (a) DC and (b) RF transconductance vs. gate bias. The peak RF gm is 20% higher than the peak DC Gm. **(b)**

Fig. 5 Plot of de-embedded (a) Re[Y<sub>21</sub>] vs  $\omega^2$  and (b) Re[Y<sub>22</sub>] vs  $\omega^2$ . The Y-intercept of  $Re[Y_{21}]$  and  $Re[Y_{22}]$  gives the RF gm and gd respectively. Bias condition: Vd= -1V and Vg=1V.

Fig. 4 (a) DC and (b) RF output conductance. Gate bias is swept from 0V to 2V with steps of 0.5V

Fig. 7 DC and RF transconductance modeled using gradual channel approximation. Vd = -1Vfor the measurement.

| Simulation Parameters                  |                        |                        |

|----------------------------------------|------------------------|------------------------|

| Parameters                             | DC                     | RF                     |

| Tox [nm]                               | 10                     |                        |

| L [nm]                                 | 750                    |                        |

| V <sub>dirac</sub> [V]                 | 0.85                   | 0.5                    |

| Rs [Ω-µm]                              | 340                    | 300                    |

| D <sub>it</sub> [/cm <sup>2</sup> /eV] | 2.3 X 10 <sup>13</sup> | 1.8 X 10 <sup>13</sup> |

[eV]

Ц Ц

the probing distance from the semiconductor oxide interface is limited to 1-2 nm.