# Experimental Determination of Quantum and Centroid Capacitance in Arsenide–Antimonide Quantum-Well MOSFETs Incorporating Nonparabolicity Effect

Ashkar Ali, Student Member, IEEE, Himanshu Madan, Student Member, IEEE, Rajiv Misra, Ashish Agrawal, Student Member, IEEE, Peter Schiffer, J. Brad Boos, Member, IEEE, Brian R. Bennett, and Suman Datta, Senior Member, IEEE

Abstract—Experimental gate capacitance  $(C_g)$  versus gate voltage data for  ${\rm InAs_{0.8}Sb_{0.2}}$  quantum-well MOSFET (QWMOSFET) is analyzed using a physics-based analytical model to obtain the quantum capacitance  $(C_Q)$  and centroid capacitance  $(C_{\rm cent})$ . The nonparabolic electronic band structure of the  ${\rm InAs_{0.8}Sb_{0.2}}$  QW is incorporated in the model. The effective mass extracted from Shubnikov–de Haas magnetotransport measurements is in excellent agreement with that extracted from capacitance measurements. Our analysis confirms that in the operational range of  ${\rm InAs_{0.8}Sb_{0.2}}$  QW-MOSFETs, quantization and nonparabolicity in the QW enhance  $C_Q$  and  $C_{\rm cent}$ . Our quantitative model also provides an accurate estimate of the various contributing factors toward  $C_g$  scaling in future arsenide–antimonide MOSFETs.

Index Terms—Effective mass, high- $\kappa$  dielectric, InAsSb, interface states, nonparabolicity, quantum capacitance, split capacitance–voltage.

### I. Introduction

IXED-ANION  $InAs_ySb_{1-y}$  quantum wells (QWs) with high electron mobility are candidates for direct integration with high hole mobility  $In_xGa_{1-x}Sb$  QW for ultralow-power complementary applications [1], [2]. However, as a direct consequence of the low effective mass for electrons in the  $\Gamma$ -valley,  $InAs_ySb_{1-y}$  QW-MOSFETs can suffer from the so-called density of states (DOS) bottleneck that may limit the effective ON-current and adversely affect switching in fixed

Manuscript received October 8, 2010; revised January 4, 2011; accepted January 16, 2011. Date of publication March 3, 2011; date of current version April 22, 2011. This work was supported in part by the Focus Center Research Program for Materials, Structures, and Devices sponsored by the Semiconductor Research Corporation and the Defense Advanced Research Projects Agency and in part by the National Science Foundation Materials Research Science and Engineering Centers under Grant DMR 0820404. The review of this paper was arranged by Editor G. Ghione.

A. Ali, H. Madan, R. Misra, A. Agrawal, P. Schiffer, and S. Datta are with The Pennsylvania State University, University Park, PA 16802 USA (e-mail: ashkar.ali@psu.edu; himanshu@psu.edu; rxm74@psu.edu; axa981@psu.edu; pes12@psu.edu; sdatta@engr.psu.edu).

J. B. Boos and B. R. Bennett are with the Naval Research Laboratory, Washington, DC 20375 USA (e-mail: boos@nrl.navy.mil; brian.bennett@nrl.navy.mil).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2110652

load capacitance dominated digital circuits [3]. The capacitance associated with the QW in  ${\rm InAs_ySb_{1-y}}$  QW-MOSFET depends on the 2-D DOS (quantum capacitance  $C_Q$ ) as well as the electron wave function distribution (centroid capacitance  $C_{\rm cent}$ ) in the QW [4]. Even though the low effective mass limits the  $C_Q$ , quantization and nonparabolicity enhance the  $C_Q$  and the  $C_{\rm cent}$  of the  ${\rm InAs_{0.8}Sb_{0.2}}$  QW [5]. Incorporation of a gate dielectric within the  ${\rm InAs_ySb_{1-y}}$  QW-MOSFET, together with finite capacitance  $C_{\rm barrier}$  arising from the upper semiconductor barrier layer, further increases the equivalent oxide thickness (EOT) in a QW-MOSFET. Hence, it is imperative to understand how the different components of capacitance  $(C_Q, C_{\rm cent}, C_{\rm barrier},$  and  $C_{\rm ox}$ ) affect the overall gate capacitance and scalability of this device.

In this paper, we present a physics-based analytical model to analyze the experimental gate capacitance  $(C_q)$  versus gate voltage  $(V_q)$  data for an InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET with a composite high- $\kappa$  gate stack (5.5 nm Al<sub>2</sub>O<sub>3</sub>–1 nm GaSb) and to systematically extract the quantum capacitance of the channel including the nonparabolicity effect, as well as the centroid capacitance associated with the spread of the electron wave function in the QW. The significance of this work lies in the fact that accurate quantification of the quantum capacitance in high mobility channel MOSFETs is critical to future device scaling. A small-signal equivalent circuit model is utilized to correct the measured gate capacitance data from the impact of the interface state density  $D_{it}$ . In a previous work done by Jin et al. [6], the quantum capacitance of a Schottky-gated InAs QWFET was analyzed, but without considering the effect of nonparabolicity in the band structure and the impact of interface states. Jin et al. used a single effective mass higher than the  $\Gamma$ -valley mass of bulk InAs to account for the increase in  $C_Q$  due to quantization and nonparabolicity. In this paper, we incorporate the nonparabolicity in the InAs<sub>0.8</sub>Sb<sub>0.2</sub> band structure using the nonparabolicity factor  $\alpha$ , which captures the energy dependence of both the 2-D DOS and the effective mass. The effective mass obtained from the capacitance modeling was further verified using Shubnikov-de Haas (SdH) magnetotransport measurements at a low temperature (2–15 K) and a high magnetic field (0-9 T). We also present an EOT scalability study that shows that for InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET with thin

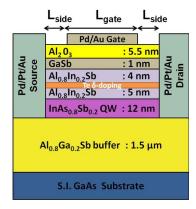

Fig. 1. Schematic of the InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET with composite high- $\kappa$  dielectric (5.5 nm Al<sub>2</sub>O<sub>3</sub>-1 nm GaSb).

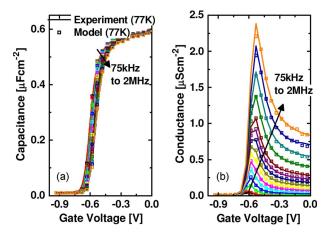

Fig. 2. Measured and modeled (a) split  $C_g-V_g$  and (b)  $G-V_g$  characteristics of an InAs $_{0.8}{\rm Sb}_{0.2}$  QW-MOSFET at 77 K.

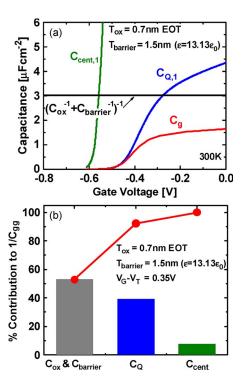

dielectric (0.7 nm EOT) and barrier (0.45 nm EOT), the oxide and barrier capacitance has similar contribution to the gate capacitance (53% of  $1/C_g$ ) as that from the quantum capacitance  $C_Q$  (39% of  $1/C_g$ ) and the centroid capacitance  $C_{\rm cent}$  (8% of  $1/C_g$ ) for a gate overdrive of 0.35 V (approximately two-thirds of  $V_{\rm DD}=0.5$  V).

# II. Experimental $C_g$ – $V_g$ Measurements and Correcting for $D_{\mathrm{it}}$

Fig. 1 shows the schematic of the fabricated InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET with 1 nm GaSb and 5.5 nm Al<sub>2</sub>O<sub>3</sub> dielectric that forms a composite gate stack on top of the barrier. The fabrication details of the transistor are reported elsewhere [7]. A thin layer of GaSb (1 nm) is used as an interfacial layer with the high- $\kappa$  dielectric to reduce the interface state density [8]. Fig. 2(a) and (b) shows the measured and modeled split  $C_q$ – $V_q$ and  $G-V_q$  characteristics of InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET at 77 K and the frequency dispersion characteristics due to the interface states. Similar analysis was done at 150 and 300 K (not shown here). The  $C_g$ – $V_g$  and G– $V_g$  data were self-consistently modeled using an equivalent circuit model that accounts for the admittance contribution from the interface states at the Al<sub>2</sub>O<sub>3</sub>-GaSb interface. The conductance response of the traps  $(G_n/\omega)$  versus frequency [7] shows positive slope with  $V_a$ , indicating electron capture/emission process. The technique for

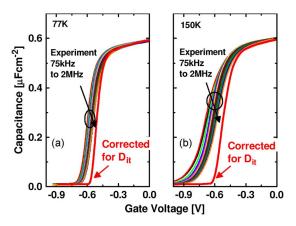

Fig. 3.  $C_g$ – $V_g$  curves corrected for  $D_{\rm it}$  along with the measured  $C_g$ – $V_g$  characteristics for (a) 77 K and (b) 150 K.

extracting the interface state density  $(D_{\rm it})$ , trap response time  $(\tau)$ , and the frequency-independent semiconductor capacitance using the equivalent circuit model is explained in detail in [9]. Fig. 3 shows the  $C_g$ – $V_g$  curves corrected for  $D_{\rm it}$  along with the measured  $C_g$ – $V_g$  characteristics for 77 and 150 K.

## III. ANALYTICAL MODELING OF GATE CAPACITANCE OF QW-MOSFET INCLUDING NONPARABOLICITY

The capacitance of the  $InAs_{0.8}Sb_{0.2}$  QW  $(C_S)$  can be expressed as a series combination of the quantum capacitance  $(C_Q)$ , which is related to the 2-D DOS in the QW, and the centroid capacitance  $(C_{cent})$ , which is related to the change in the subband energy levels in the QW due to the sheet charge density in the QW, as given by

$$C_S = \frac{\partial(-Q_S)}{\partial\psi_{S,QW}} = \sum_i q \frac{\partial N_{S,i}}{\partial\psi_{S,QW}}$$

(1)

$$N_S = \sum_{i} N_{S,i} = \sum_{i} \int_{E_i}^{\infty} DOS_{2D}(E) f(E) dE$$

(2)

$$q\partial\psi_{S,QW} = \partial(E_F - E_C) = \partial(E_F - E_i) + \partial(E_i - E_C)$$

(3)

$C_S = \sum_{i} q^2 \frac{\partial N_{S,i}}{\partial (E_F - E_i) + \partial (E_i - E_C)} \tag{4}$

$$C_S = \sum_{i} q^2 \frac{\partial N_{S,i}}{\partial (E_F - E_i)} \frac{\partial (E_F - E_i)}{\partial (E_F - E_i) + \partial (E_i - E_C)}$$

(5)

$C_S = \sum_{i} C_{S,i} \tag{6}$

$$\frac{1}{C_{S,i}} = \frac{1}{C_{Q,i}} + \frac{1}{C_{Q,i}} \frac{\partial (E_i - E_C)}{\partial (E_F - E_i)} = \frac{1}{C_{Q,i}} + \frac{1}{C_{\text{cent},i}}$$

$$C_{Q,i} = q^2 \frac{\partial N_{S,i}}{\partial (E_F - E_i)}; \quad C_{\text{cent},i} = C_{Q,i} \frac{\partial (E_F - E_i)}{\partial (E_i - E_C)}$$

(8)

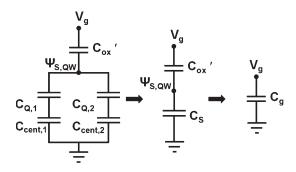

Fig. 4. Equivalent circuit model of a QW-MOSFET showing the different components of gate capacitance.  $C_{Q,i}$  stands for quantum capacitance of the ith subband,  $C_{\mathrm{cent},i}$  stands for centroid capacitance of the ith subband of  $C_{\mathrm{cont},i}$  stands for the series combination of oxide and barrier capacitance, and  $\Psi_{S,\mathrm{QW}}$  stands for the quantum well potential. Only two subbands are considered in the model.

where,  $N_{S,i}$  stands for charge density in the ith subband,  $\Psi_{S,\mathrm{QW}}$  stands for the QW potential,  $C_{Q,i}$  stands for quantum capacitance of the ith subband,  $C_{\mathrm{cent},i}$  stands for centroid capacitance of the ith subband,  $E_i-E_C$  stands for the position of the ith subband with respect to the bottom of the conduction band in the QW,  $E_F-E_i$  stands for the Fermi level position with respect to the ith subband, and f(E) is the Fermi-Dirac distribution function.

The nonparabolicity of the InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW band structure is included in the model by modifying the effective mass and 2-D DOS using the nonparabolicity factor  $\alpha$  as follows:

$$m^* = \frac{\hbar^2 k}{\partial E/\partial k} = m_{\Gamma} (1 + 2\alpha E) \tag{9}$$

$$DOS_{2-D} = \frac{m^*}{\pi \hbar^2} = \frac{m_{\Gamma}(1 + 2\alpha E)}{\pi \hbar^2}$$

(10)

where  $m_{\Gamma}$  is the effective mass at the bottom of the  $\Gamma$ -valley, and E is the total energy with respect to the bottom of the  $\Gamma$ -valley [10].

Fig. 4 shows the equivalent circuit model showing the different components of the gate capacitance. The extraction of  $C_{\rm cent}$  requires solving Schroedinger and Poisson equations self-consistently to evaluate the subband energy levels  $(E_i-E_C)$  as a function of charge density. We have performed Nextnano [11] simulations to obtain  $E_i-E_C$  as a function of  $E_F-E_i$ . Using the QW capacitance evaluated from (6), the gate capacitance is obtained using

$$\frac{1}{C_g} = \frac{1}{C_{\text{ox}}} + \frac{1}{C_{\text{barrier}}} + \frac{1}{C_S} \tag{11}$$

where  $C_{\rm barrier}$  and  $C_{\rm ox}$  are the barrier and oxide capacitance, respectively.

The gate capacitance obtained in (11) is a function of the potential  $(\Psi_{S,\mathrm{QW}})$  in the QW. The applied gate potential is calculated from  $\Psi_{S,\mathrm{QW}}$  using the equivalent circuit model shown in Fig. 4.

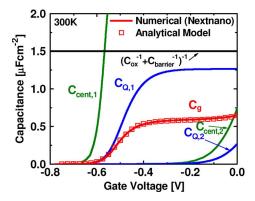

Fig. 5 shows analytical modeling of gate capacitance of  $InAs_{0.8}Sb_{0.2}$  QW-MOSFET with the numerical simulations (Nextnano). The effective mass at the bottom of  $\Gamma$ -valley is taken to be  $0.018m_0$  for  $InAs_{0.8}Sb_{0.2}$  [12]. The analytical model shows excellent agreement with the numerical simula-

Fig. 5. Analytical modeling of gate capacitance of an  $InAs_{0.8}Sb_{0.2}$  QW-MOSFET compared with numerical simulations (Nextnano).

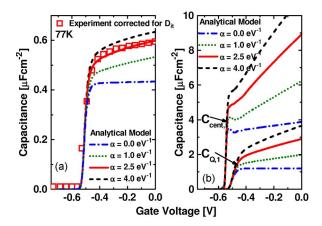

Fig. 6. Effect of varying  $\alpha$  on (a) the gate capacitance at 77 K and (b) the quantum and centroid capacitance at 77 K. Best fit to the experimental data was obtained with  $\alpha=2.5~{\rm eV}^{-1}$ .

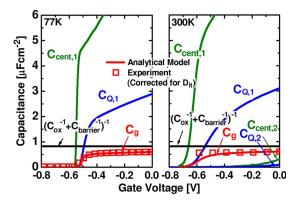

tion. This validation was first done for a parabolic band structure case ( $\alpha = 0$ ). The subband positions for evaluating the centroid capacitance were numerically obtained as a function of the Fermi level from Nextnano simulations for all the cases considered in this paper. Now, we incorporate the nonparabolicity of the band structure in our analytical calculations to model and analyze the experimental  $C_q$ – $V_q$  data obtained from the  $InAs_{0.8}Sb_{0.2}$  QW-MOSFET after  $\mathcal{D}_{it}$  correction. Fig. 6(a) shows the experimental  $C_g$ – $V_g$  data corrected for  $D_{\mathrm{it}}$  at 77 K, along with the analytical model. The effect of varying  $\alpha$ on the different components of gate capacitance is also shown in Fig. 6. For single effective mass approximation ( $\alpha = 0$ ), the quantum capacitance will not change with gate bias as the Fermi level moves above the first subband in the QW. This is due to the constant DOS in the QW, and  $C_Q$  reaches the quantum capacitance limit. Increasing  $\alpha$  gives rise to increasing  $C_Q$ , even after the Fermi level moves above the first subband. Hence, the  $C_Q$  and the  $C_{cent}$  will keep increasing with gate bias. The best fit to the experimental data was obtained with  $\alpha = 2.5 \text{ eV}^{-1}$  at both 77 and 150 K. Fig. 7(a) and (b) shows the different components of the gate capacitance for the 77 and 300 K  $C_q$ – $V_q$  data. There is additional voltage stretch-out in the 300 K  $C_q$ – $V_q$  data, even after correcting for  $D_{\rm it}$ , most likely due to hole accumulation in the GaSb barrier layer. Hence, we modeled only a portion of the 300 K  $C_g$ – $V_g$  data in Fig. 7(b).

Fig. 7. Components of the gate capacitance for (a) the 77 K, and (b) the 300 K  $C_g$ – $V_g$  data. Additional voltage stretch-out in the 300 K  $C_g$ – $V_g$  data, even after correcting for  $D_{\rm it}$ , is most likely due to accumulation of holes in the Al<sub>0.8</sub>In<sub>0.2</sub>Sb barrier layer.

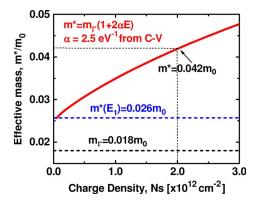

Fig. 8. Effective mass extracted from the  $C_g$ – $V_g$  analysis as a function of charge density in the QW.

Fig. 8 shows the effective mass extracted from the  $C_g - V_g$  analysis as a function of charge density in the QW. For a charge density of  $2.0 \times 10^{12}~{\rm cm}^{-2}$ , the extracted effective mass is  $0.042m_0$ , which is 2.33 times higher than  $m_\Gamma$   $(0.018m_0)$  due to quantization and nonparabolicity. The nonparabolicity factor extracted from  $C_g - V_g$  analysis ( $\alpha = 2.5~{\rm eV}^{-1}$ ) is similar to that for the InAs/AlSb QW heterostructure ( $\alpha = 2.5~{\rm eV}^{-1}$ ) reported from cyclotron resonance measurements [13].

### IV. SdH Analysis for Effective Mass Extraction

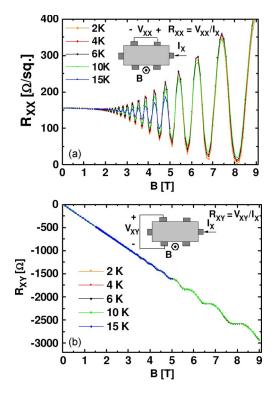

The effective mass obtained from the capacitance modeling was verified using SdH magnetotransport measurements on an InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW heterostructure (without dielectric) at low temperatures (2–15 K) and high magnetic fields (0–9 T). The magnetotransport measurements, in standard four-probe DC configuration, were carried out using Quantum Design Model 6000 Physical Property Measurement System, with a base temperature of 1.8 K and magnetic field in the range of 0–9 T. Fig. 9(a) and (b) shows the measured sheet resistance ( $R_{\rm XX}$ ) and Hall resistance ( $R_{\rm XY}$ ) of the device from 0 to 9 T. The insets in the figures show the configurations to measure  $R_{\rm XX}$  and  $R_{\rm XY}$ . SdH oscillations are observed in  $R_{\rm XX}$  at magnetic fields below 8 T. At fields above 8 T, the quantum Hall plateaus appear in  $R_{\rm XY}$ , and  $R_{\rm XX}$  tends to zero resistance. The

Fig. 9. (a) Measured sheet resistance  $(R_{\rm XX})$  and (b) Hall resistance  $(R_{\rm XY})$  of the InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW heterostructure from 0 to 9 T. Insets in the figures show the configurations employed to measure  $R_{\rm XX}$  and  $R_{\rm XY}$ .

magnetic field and temperature dependence of sheet resistance can be expressed as [14]–[16]

$$\frac{\Delta \rho_{\rm XX}}{\rho_0} = R_S \frac{4\chi}{\sinh \chi} \exp\left(\frac{-\pi}{\omega_c \tau_q}\right) \cos\left(2\pi \frac{E_F}{\hbar \omega_c} + \phi\right) \quad (12)$$

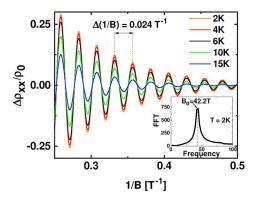

where  $\rho_0$  is the sheet resistance at zero B,  $\tau_q$  is the quantum lifetime,  $\chi = 2\pi^2 kT/\hbar\omega_c$ , and  $\omega_c = eB/m^*$  is the cyclotron frequency. The prefactor  $R_s$  is associated with Zeeman splitting and is assumed to be independent of the magnetic field in the following analysis [14]. While extracting the effective mass from SdH oscillations, the background magnetoresistance was corrected as follows. The envelope of maxima (minima) of the  $\rho_{\rm XX}$  oscillations was evaluated from the peak (valley) in the  $\rho_{\rm XX}$  as a function of B. The average of the two envelopes gave the background magnetoresistance that was subtracted from the measured  $\rho_{XX}$ . Fig. 10 shows the periodic SdH oscillations in  $\Delta \rho_{\rm XX}/\rho_0$  (after removing the background contribution) as a function of 1/B. FFT of  $\Delta \rho_{\rm XX}/\rho_0$  versus 1/B is shown in Fig. 10 (inset). There is a well resolved peak at the fundamental oscillation period  $B_0 = 42.2$  T. From the period of oscillation,  $\Delta(1/B)=0.024\,\mathrm{T}^{-1}$ , the sheet carrier density can be obtained as  $N_S=2q/h\Delta(1/B)=2.01\times10^{12}\,\mathrm{cm}^{-2}$ . The carrier density obtained from period of SdH oscillations is independent of the device dimensions or QW thickness.

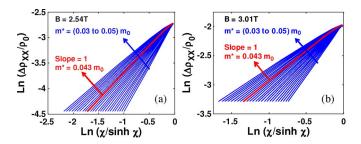

The analytical procedure to extract the effective mass is as follows. From (12), a plot of  $\ln(\Delta\rho_{\rm XX}/\rho_0)$  versus  $\ln(\chi/\sinh\chi)$  gives a straight line with slope = 1.  $\ln(\Delta\rho_{\rm XX}/\rho_0)$  is from the experimentally measured magnetoresistance data as a function of temperature, and  $\ln(\chi/\sinh\chi)$  is calculated as a function of temperature using  $m^*$  as an

Fig. 10. Periodic SdH oscillations in  $\Delta \rho_{\rm XX}/\rho_0$  (after removing the background contribution) as a function of 1/B. Fast Fourier transform of  $\Delta \rho_{\rm XX}/\rho_0$  versus 1/B is shown in the inset.

Fig. 11. Plot of  $\ln(\Delta \rho_{\rm XX}/\rho_0)$  versus  $\ln(\chi/\sinh\chi)$  for (a) B=2.54 T and (b) B=3.01 T to extract effective mass. Correct value of effective mass gives a slope of 1 for the graph.

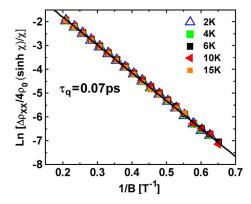

Fig. 12. Dingle plot used to extract quantum lifetime.

adjustable parameter. The correct value of  $m^*$  gives a slope of 1 for the graph. Fig. 11 shows the extraction procedure at  $B = 2.54 \,\mathrm{T}$  and  $B = 3.01 \,\mathrm{T}$ . The extracted effective mass from the analysis is  $0.043m_0$  at a sheet carrier density of  $2.01 \times$  $10^{12}$  cm<sup>-2</sup> (from the period of SdH oscillations). Fig. 12 shows the Dingle plot [17] of  $\ln((\Delta \rho_{XX}/\rho_0)(\sinh \chi/4\chi))$  versus 1/Busing  $m^* = 0.043m_0$ , which gives a universal straight line for all temperatures, as given by (12). The slope of the line is  $-\pi m^*/q\tau_q$ , which yields a quantum lifetime of  $\tau_q = 0.065$  ps. The assumption that  $R_s$  is independent of the magnetic field is justified from Figs. 11 and 12, which give good straight lines as expected from (12). The ratio of transport time  $\tau = 0.5$  ps obtained from QW electron mobility at 2 K to the quantum scattering time is  $\sim$ 7.5. This indicates that the dominant scattering mechanism in the InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW heterostructure (without a dielectric) at low temperatures is due to the ionized impurities

Fig. 13. (a) Components of the gate capacitance of  $InAs_{0.8}Sb_{0.2}$  QW-MOSFET with a scaled dielectric and barrier and (b) percentage contribution of various components of gate capacitance to  $1/C_g$ .

in the  $In_{0.2}Al_{0.8}Sb$  barrier or interface charge at the barrier–QW interface, as observed in the case of the  $GaAs/Al_xGa_{1-x}As$  QW heterostructure [18].

### V. QW-MOSFET GATE CAPACITANCE SCALING PROJECTION

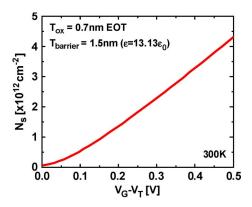

In this section, we provide a quantitative estimate of the various factors determining gate capacitance scaling in future arsenide-antimonide QW-MOSFETs. As shown in the previous sections, both the quantization and the nonparabolicity increase the effective mass in the QW, which increases the quantum capacitance  $C_Q$  and the centroid capacitance  $C_{\text{cent}}$ . As we scale the gate length of future generation QW-MOSFETs, we need to scale the thickness of the semiconductor barrier and the QW. Thinner QWs will exhibit higher  $C_{\rm cent}$  due to less change in the subband energy levels with Fermi level position [19], and higher  $C_Q$  as well due to increased DOS at higher energy, for a given sheet carrier density  $N_s$  in the QW. Fig. 13(a) and (b) shows the various components of the gate capacitance of InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET, with a 5-nm-thick QW, a 1.5-nm-thick In<sub>0.2</sub>Al<sub>0.8</sub>Sb barrier (0.45 nm EOT), and a thin high- $\kappa$  dielectric (0.7 nm EOT) on top of the barrier. For a gate overdrive of 0.35 V (approximately two-thirds of  $V_{\rm DD} = 0.5$  V), the oxide and barrier capacitance together contribute to about half (53%) of  $1/C_q$ , whereas the quantum and centroid capacitance contribute to the remaining half, with  $C_Q$  (39% of  $1/C_q$ ) being a more limiting factor than  $C_{cent}$ (8% of  $1/C_g$ ). The charge density in the QW for 0.35 V gate overdrive is  $\sim 3.5 \times 10^{12}$  cm<sup>-2</sup> (Fig. 14). This implies that the oxide and barrier capacitance are as significant as quantum

Fig. 14. Sheet charge density in the quantum well as a function of gate overdrive for  $InAs_{0.8}Sb_{0.2}$  QW-MOSFET with a scaled oxide and barrier. The threshold voltage is defined at the gate bias for which  $N_s = 5 \times 10^{10}$  cm<sup>-2</sup>.

capacitance for gate capacitance scaling in MOS-QWFETs in the arsenide-antimonide material system.

### VI. CONCLUSION

In this paper, we have presented a physics-based analytical model to extract the quantum capacitance and nonparabolicity factor in InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET. The effective mass extracted from  $C_q$ - $V_q$  analysis is validated through SdH measurements at low temperature (2-15 K) and high magnetic field (0–9 T). The effective mass of  $0.043m_0$  was obtained at  $N_s = 2.0 \times 10^{12} \text{ cm}^{-2}$  (from SdH as well as  $C_q$ – $V_q$  analysis), which is 2.33 times higher than the  $\Gamma$ -valley mass of bulk InAs<sub>0.8</sub>Sb<sub>0.2</sub>. A nonparabolicity factor of 2.5 eV<sup>-1</sup> was obtained from  $C_q$ – $V_q$  modeling. Gate capacitance scaling study of InAs<sub>0.8</sub>Sb<sub>0.2</sub> QW-MOSFET, with a 5-nm-thick QW, a 1.5-nmthick  $In_{0.2}Al_{0.8}Sb$  barrier (0.45 nm EOT), and a thin high- $\kappa$ oxide (0.7 nm EOT) shows that the oxide and barrier capacitance limit the gate capacitance (53% of  $1/C_q$ ) more than the  $C_Q$  (39% of  $1/C_g$ ) and the  $C_{\rm cent}$  (8% of  $1/C_g$ ) for a gate overdrive of 0.35 V (approximately two-thirds of  $V_{\rm DD} =$ 0.5 V).

### ACKNOWLEDGMENT

A. Ali would like to thank IBM for the Ph.D. Fellowship Award in 2010 and A. Majumdar of IBM Research for the valuable discussions.

### REFERENCES

- [1] B. R. Bennett, R. Magno, J. B. Boos, W. Kruppa, and M. G. Ancona, "Antimonide-based compound semiconductors for electronic devices: A review," *Solid State Electron.*, vol. 49, no. 12, pp. 1875–1895, Dec. 2005.

- [2] J. B. Boos, B. R. Bennett, N. A. Papanicolaou, M. G. Ancona, J. G. Champlain, R. Bass, D. Park, B. V. Shanabrook, Y. C. Chou, M. G. Lange, and J. M. Yang, "Sb-based heterostructure device technology for high-speed, low-power applications," *IEICE Trans. Electron.*, vol. E91-C, no. 7, Jul. 2008.

- [3] M. Rodwell, W. Frensley, S. Steiger, E. Chagarov, S. Lee, H. Ryu, Y. Tan, G. Hegde, L. Wang, J. Law, T. Boykin, G. Klimek, P. Asbeck, A. Kummel, and J. N. Schulman, "III–V FET channel designs for high current densities and thin inversion layers," in *Proc. DRC*, Jun. 21–23, 2010, pp. 149–152.

- [4] S. Luryi, "Quantum capacitance devices," Appl. Phys. Lett., vol. 52, no. 6, pp. 501–503, Feb. 1988.

- [5] B. R. Nag and S. Mukhopadhyay, "In-plane effective mass in narrow quantum wells of nonparabolic semiconductors," *Appl. Phys. Lett.*, vol. 62, no. 19, pp. 2416–2418, May 1993.

- [6] D. Jin, D. Kim, T. Kim, and J. A. del Alamo, "Quantum capacitance in scaled down III–V FETs," in *IEDM Tech. Dig.*, Dec. 7–9, 2009, pp. 1–4.

- [7] A. Ali, H. Madan, R. Misra, E. Hwang, A. Agrawal, I. Ramirez, P. Schiffer, T. N. Jackson, S. E. Mohney, J. B. Boos, B. R. Bennett, I. Geppert, M. Eizenberg, and S. Datta, "Advanced composite high-κ gate stack for mixed anion arsenide–antimonide quantum well transistors," in *IEDM Tech. Dig.*, Dec. 6–8, 2010, pp. 6.3.1–6.3.4.

- [8] A. Ali, H. S. Madan, A. P. Kirk, R. M. Wallace, D. A. Zhao, D. A. Mourey, M. K. Hudait, T. N. Jackson, B. R. Bennett, J. B. Boos, and S. Datta, "Fermi level unpinning of GaSb(100) using plasma enhanced ALD Al<sub>2</sub>O<sub>3</sub> dielectric," *Appl. Phys. Lett.*, vol. 97, no. 14, pp. 143 502(1)–143 502(3), Oct. 2010.

- [9] A. Ali, H. Madan, S. Koveshnikov, S. Oktyabrsky, R. Kambhampati, T. Heeg, D. Schlom, and S. Datta, "Small-signal response of inversion layers in high-mobility  $In_{0.53}Ga_{0.47}As$  MOSFETs made with thin high- $\kappa$  dielectrics," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 742–748, Apr. 2010.

- [10] V. A. Altschul, A. Fraenkel, and E. Finkman, "Effects of band nonparabolicity on two-dimensional electron gas," *J. Appl. Phys.*, vol. 71, no. 9, pp. 4382–4384, May 1992.

- [11] S. Birner, T. Zibold, T. Andlauer, T. Kubis, M. Sabathil, A. Trellakis, and P. Vogl, "Nextnano: General purpose 3-D simulations," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2137–2142, Sep. 2007.

- [12] I. Vurgaftman, J. R. Meyer, and L. R. Ram-Mohan, "Band parameters for III–V compound semiconductors and their alloys," *J. Appl. Phys.*, vol. 89, no. 11, pp. 5815–5875, Jun. 2001.

- [13] J. Scriba, A. Wixforth, J. P. Kotthaus, C. Bolognesi, C. Nguyen, and H. Kroemer, "Spin- and Landau-splitting of the cyclotron resonance in a nonparabolic two-dimensional electron system," *Solid State Commun.*, vol. 86, no. 10, pp. 633–636, Jun. 1993.

- [14] T. E. Whall, N. L. Mattey, A. D. Plews, P. J. Phillips, O. A. Mironov, R. J. Nicholas, and M. J. Kearney, "Effective mass and quantum lifetime in a Si/Si<sub>0.87</sub>Ge<sub>0.13</sub>/Si two-dimensional hole gas," *Appl. Phys. Lett.*, vol. 64, no. 3, pp. 357–359, Jan. 1994.

- [15] T. Ando, A. B. Fowler, and F. Stern, "Properties of 2-dimensional electron system," Rev. Mod. Phys., vol. 54, no. 2, pp. 437–672, Apr.–Jun. 1982.

- [16] F. B. Mancoff, L. J. Zielinski, C. M. Marcus, K. Campman, and A. C. Gossard, "Shubnikov-de Haas oscillations in a two-dimensional electron gas in a spatially random magnetic field," *Phys. Rev. B, Condens. Matter*, vol. 53, no. 12, pp. R7 599–R7 602, Mar. 1996.

- [17] R. B. Dingle, "Some magnetic properties of metals—Part 2: The influence of collisions on the magnetic behaviour of large systems," *Proc. R. Soc. Lond. A, Math. Phys. Sci.*, vol. 211, no. 1107, pp. 517–525, Mar. 1952.

- [18] P. T. Coleridge, "Small-angle scattering in two-dimensional electron gases," *Phys. Rev. B, Condens. Matter*, vol. 44, no. 8, pp. 3793–3801, Aug. 1991.

- [19] H. S. Pal, K. D. Cantley, S. S. Ahmed, and M. S. Lundstrom, "Influence of bandstructure and channel structure on the inversion layer capacitance of silicon and GaAs MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 3, pp. 904–908, Mar. 2008.

Ashkar Ali (S'09) received the B.S. degree in materials science and engineering from the Indian Institute of Technology, Madras, India, in 2007 and the M.S. degree in engineering science from the Pennsylvania State University, University Park, in 2009, where he is currently working toward the Ph.D. degree in electrical engineering in the Department of Electrical Engineering.

His research interests include oxide and III-V interface characterization and simulation, fabrication, and characterization of narrow-gap quantum-well

FETs for beyond silicon technology nodes.

Mr. Ali is a recipient of the 2010–2011 IBM Ph.D. Fellowship Award.

Himanshu Madan (S'09) received the B.S. degree in electronics and telecommunications engineering from the College of Engineering, Pune, India, in 2008. He is currently working toward the M.S. degree in electrical engineering in the Department of Electrical Engineering, Pennsylvania State University, University Park.

His research interests include small-signal response of minority and majority carriers in III–V channel FETs with high- $\kappa$  gate stacks up to the gigahertz frequency domain.

Rajiv Misra received the B.S. degree in physics and the M.S. degree in computer applications (scientific parallel computing) from the Indian Institute of Technology, Delhi, India, in 1999 and 2002, respectively, and the Ph.D. degree in physics from University of Florida, Gainesville, in 2009. He is currently doing postdoctoral studies in the Department of Physics, Pennsylvania State University, University Park.

His research interests include novel magnetic oxides, geometrically frustrated magnets, magnetic

nanoparticles, and electronic transport in mesoscopic systems.

Ashish Agrawal (S'10) received the B.Tech. degree in electronics and communication engineering from the Visvesvaraya National Institute of Technology, Nagpur, India, in 2009. He is currently working toward the M.S. degree in electrical engineering in the Department of Electrical Engineering, Pennsylvania State University, University Park.

His research interests include transport modeling in III-V channel FETs for high performance and oxide/III-V interface characterization and modeling.

Peter Schiffer received the B.S. degree from Yale University, New Haven, CT, in 1988 and the Ph.D. degree from Stanford University, Stanford, CA, in 1993.

He is a Professor of Physics and also the Associate Vice President for Research and Director of Strategic Initiatives in the Office of the Vice President for Research at Pennsylvania State University, University Park. Previously, he held a faculty appointment at the University of Notre Dame, Notre Dame, IN, from 1995 to 2000, and was with AT&T Bell Laboratories

from 1993 to 1995. He is the author of more than 160 published papers. His research focuses on geometrically frustrated magnets, magnetic semiconductors and oxides, magnetic nanostructures, and granular materials.

Dr. Schiffer is a Fellow of the American Physical Society. He has served as the Chair of the American Physical Society Topical Group on Magnetism and its Applications and as the Program Chair of the 2007 Conference on Magnetism and Magnetic Materials. He will assume the role of Chair of the American Physical Society Division of Materials Physics in 2011. He is the recipient of a Career Award from the National Science Foundation, a Presidential Early Career Award for Scientists and Engineers from the Army Research Office, an Alfred P. Sloan Research Fellowship, and the Faculty Scholar Medal in the Physical Sciences and the Joel and Ruth Spira Award for Teaching Excellence from Penn State.

**J. Brad Boos** (M'85) received the B.S. degree in chemistry from the University of Maryland, College Park, in 1977, and the M.S. degree in electrical engineering from The George Washington University, Washington, DC, in 1987.

Since 1980, he has been with the research staff in the Electronics Science and Technology Division, Naval Research Laboratory, Washington, DC, where he has worked on III–V microwave and millimeterwave device development, and has been the Head of the High-Speed Low-Power Devices Section since

2002. His research efforts have included the design, the fabrication, and the characterization of InP-based high-electron-mobility transistors (HEMTs) and photodetectors, Sb-based HEMTs, p-channel heterojunction field-effect transistors, heterojunction bipolar transistors, and quantum devices.

Mr. Boos has served on the Technical Program Committee and Steering Committee of the InP and Related Materials (IPRM) Conference and served as the Program Chair for the 2000 IPRM Conference. He has also served on the Technical Program Committee of the International Semiconductor Device Research Symposium.

Brian R. Bennett received the B.S. and M.S. degrees in geophysics from the Massachusetts Institute of Technology. He then served as a military officer in the Air Force's Solid State Sciences Division from 1984 to 1988. His research included electro-optic effects in Si and group III-V semiconductors and low-temperature deposition of silicon dioxide. In 1992, he received the Ph.D. degree in Materials Science and Engineering from M.I.T. Since 1992, Dr. Bennett has been at the Naval Research Laboratory in Washington, DC, where he currently serves

as head of the Nanotechnology Section. His research focuses on the epitaxial growth and applications of antimonide and arsenide semiconductor heterostructures, including n-channel InAs high-electron-mobility transistors and p-channel InGaSb field-effect transistors. He serves on the Electronic Materials Committee and is a member of the American Physical Society.

Suman Datta (SM'06) received the B.S. degree in electrical engineering from the Indian Institute of Technology, Kanpur, India, in 1995 and the Ph.D. degree in electrical and computer engineering from the University of Cincinnati, Cincinnati, OH, in 1999.

He is an Associate Professor in the Department of Electrical Engineering, Pennsylvania State University, University Park. From 1999 to 2007, as a member of the Logic Technology Development and Components Research Group at Intel Corporation, he was instrumental in the demonstration of the

world's first indium—antimonide based quantum-well transistors operating at room temperature with a record power-delay product, the first experimental demonstration of metal gate plasmon screening and channel strain engineering in high-rs/metal-gate CMOS transistors, and the investigation of the transport properties and the electrostatic robustness in nonplanar "trigate transistors" for extreme scalability. Since 2007, he has been with Pennsylvania State University as the Joseph Monkowsky Professor for Early Faculty Career Development, exploring new materials, novel nanofabrication techniques, and nonclassical device structures for CMOS "enhancement" as well as "replacement" for future energy-efficient computing applications. He is the author of over 65 archival refereed journal and conference papers. He is the holder of 91 U.S. patents.