## Experimental Staggered-Source and N+ Pocket-Doped Channel III–V Tunnel Field-Effect Transistors and Their Scalabilities

Dheeraj Mohata, Saurabh Mookerjea, Ashish Agrawal, Yuanyuan Li, Theresa Mayer, Vijaykrishnan Narayanan<sup>1</sup>, Amy Liu<sup>2</sup>, Dmitri Loubychev<sup>2</sup>, Joel Fastenau<sup>2</sup>, and Suman Datta

Department of Electrical Engineering, Pennsylvania State University, University Park, PA 16802, U.S.A. <sup>1</sup>Department of Computer Science and Engineering, Pennsylvania State University, University Park, PA 16802, U.S.A. <sup>2</sup>IQE Inc., Bethlehem, PA 18015, U.S.A.

Received December 8, 2010; accepted January 22, 2011; published online February 9, 2011

In this paper, we experimentally demonstrate 100% enhancement in drive current ( $l_{ON}$ ) over In<sub>0.53</sub>Ga<sub>0.47</sub>As n-channel homojunction tunnel fieldeffect transistor (TFET) by replacing In<sub>0.53</sub>Ga<sub>0.47</sub>As source with a moderately staggered and lattice-matched GaAs<sub>0.5</sub>Sb<sub>0.5</sub>. The enhancement is also compared with In<sub>0.53</sub>Ga<sub>0.47</sub>As N+ pocket ( $\delta$ )-doped channel homojunction TFET. Utilizing calibrated numerical simulations, we extract the effective scaling length ( $\lambda_{eff}$ ) for the double gate, thin-body configuration of the staggered heterojunction and  $\delta$ -doped channel TFETs. The extracted  $\lambda_{eff}$  is shown to be lower than the geometrical scaling length, particularly in the highly staggered-source heterojunction TFET due to the reduced channel side component of the tunnel junction width, resulting in improved device scalability. © 2011 The Japan Society of Applied Physics

unnel field-effect transistors (TFETs) have gained tremendous interest recently owing to their potential in achieving sub-kT/q steep switching slope (SS) at room temperature (RT) and thus enabling higher on-current for a given on-state-to-off-state current ratio at very low supply voltages.<sup>1-9)</sup> However, due to the relatively large tunneling barrier  $(E_b)$  and width, silicon, germanium, and III-V based homojunction TFETs (Homj-TFETs) still face major challenges in demonstrating metal-oxide-semiconductor field-effect-transistor-like large drive currents  $(I_{ON})$ which is a prime requirement for any high-performance logic application.<sup>1,6)</sup> It has been theoretically shown that  $I_{ON}$ can be further enhanced over Homj-TFET by employing i) a staggered heterojunction source or ii) an N+ pocket  $(\delta)$ -doped channel, without paying any penalty for ambipolar leakage.<sup>6,8)</sup> However, for either case, a complementary experimental demonstration is absent in the category of III-V-based TFETs which form a natural choice for enhancing the on-current  $(I_{ON})$  with the availability of a large pool of lattice-matched, narrow-gap, and small-tunneling-mass semiconductors having different band-edge alignments.

In this work, we provide separate demonstrations of  $I_{\rm ON}$ enhancement over n-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As Homj-TFET by a) replacing the In<sub>0.53</sub>Ga<sub>0.47</sub>As source with lattice-matched, staggered GaAs<sub>0.5</sub>Sb<sub>0.5</sub> (Hetj-TFET) and b) putting a thin  $\delta$ -doped layer within the channel adjacent to the p+ source ( $\delta$ -doped TFET). Both techniques result in a 100% (2×) increase in  $I_{\rm ON}$  over Homj-TFET at  $V_{\rm DS} = 0.75$  V and  $V_{\rm GS} = 2$  V with the Hetj-TFET exhibiting a high  $I_{\rm ON}$  of 60  $\mu$ A/ $\mu$ m at  $V_{\rm GS} = 2.5$  V. Using two dimensional numerical simulations,<sup>12)</sup> we compare the scalability of staggeredsource Hetj-TFET,  $\delta$ -doped TFET and Homj-TFET using ultrathin-body double-gate (UTB-DG) device configuration operating at supply voltage of 0.5 V.

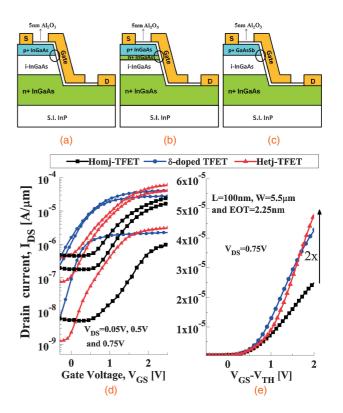

Figures 1(a)–1(c) show cross-sectional schematic of the fabricated vertical n-channel Homj, Hetj and  $\delta$ -doped TFET devices. The layers were epitaxially grown using molecular beam epitaxy (MBE) on a semi-insulating indium phosphide (InP) substrate. The P+ source regions comprise of 60-nm-thick In<sub>0.53</sub>Ga<sub>0.47</sub>As and GaAs<sub>0.5</sub>Sb<sub>0.5</sub> layer for the Homj- and Hetj-TFETs, respectively, both carbon doped at 10<sup>20</sup>/cm<sup>3</sup>. The 100 nm channel consists of intrinsically doped In<sub>0.53</sub>Ga<sub>0.47</sub>As. For  $\delta$ -doped TFET, an ultrathin 3-nm-

**Fig. 1.** (a–c) Cross sectional schematics of the fabricated InGaAs Homj-TFET,  $\delta$ -doped-TFET, and GaAsSb source Hetj-TFET respectively (L = 100 nm,  $W = 5.5 \,\mu\text{m}$  and EOT = 2.25 nm). (d) Measured  $I_d-V_g$ characteristics at  $V_{\text{DS}}$  of 0.05, 0.5, and 0.75 V. (e)  $I_d-V_g$  comparison at  $V_{\text{DS}} = 0.75 \text{ V}$  on a linear scale with the turn-on voltages normalized to that of the Homj-TFET. Both moderately staggered Hetj-TFET and  $\delta$ -doped TFET show 100% (2×)  $I_{\text{ON}}$  enhancement over Homj-TFET at  $V_{\text{GS}} = 2 \text{ V}$ .

thick  $In_{0.53}Ga_{0.47}As$  layer adjacent to the source, doped n-type with Si at  $5 \times 10^{19}/\text{cm}^3$ , is incorporated within the 100 nm channel of the Homj-TFET to form the N+ pocket. The N+ drain region is formed by 300-nm-thick  $In_{0.53}$ -Ga<sub>0.47</sub>As layer, doped with Si at  $10^{19}/\text{cm}^3$ .

The epilayers were patterned into a vertical mesa structure using  $BCl_3/Ar$  based reactive ion etching (RIE) followed by a conformal deposition of a 5-nm-thick plasma-enhanced atomic-layer-deposited (PEALD) high-*k* dielectric (Al<sub>2</sub>O<sub>3</sub>) at 200 °C.<sup>10</sup> Electron beam evaporation and lift-off techniques were used to form the sidewall gate (Pd/Au)

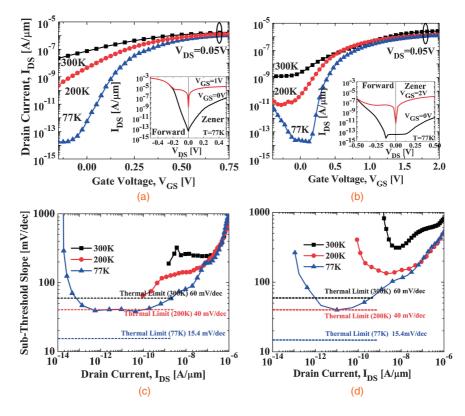

Fig. 2. (a, b)  $I_d-V_g$  at different temperatures for  $\delta$ -doped-TFET and Hetj-TFET respectively at  $V_{DS} = 0.05$  V. Insets show output characteristics at 77 K. NDR in the forward side confirms tunneling mechanism in respective devices. (c, d) Point SS plotted as a function of drain current at different temperatures for the  $\delta$ -doped-TFET and Hetj-TFET, respectively.

electrode as well as the source/drain (Ti/Pd/Au) contacts. Finally, device isolations were performed using consecutive steps of RIE (for the removal of oxide) and citric acid-based wet etch all the way to the semi-insulating InP substrate.

Figure 1(c) shows the experimental RT transfer characteristics  $(I_d-V_g)$  of the Homj-TFET,  $\delta$ -doped TFET and Hetj-TFETs at V<sub>DS</sub> of 0.05, 0.5, and 0.75 V. Hetj-TFET exhibits maximum  $I_{\rm ON}$  of  $60\,\mu A/\mu m$  at  $V_{\rm DS} = 0.75\,V$  and  $V_{\rm GS} = 2.5 \,\rm V$ , the highest value measured till date in any III-V material system in the category of tunnel FETs even with an equivalent oxide thickness (EOT) of 2.25 nm.<sup>5)</sup> Both  $\delta$ -doped TFET and Hetj-TFET turn-on at a lower gate voltage  $(V_g)$ , compared with the Homj-TFET (fabricated with the same process flow) and, hence, we normalize the gate voltage with respect to the turn-on voltage in order to benchmark the two devices. Figure 1(d) shows the  $I_d-V_g$ comparison at  $V_{\text{DS}} = 0.75$  V. At  $V_{\text{GS}} = 2$  V, both Hetj-TFET and  $\delta$ -doped TFET with  $I_{ON} \sim 46 \,\mu A/\mu m$  show 100% (2×) enhancement over the Homj-TFET ( $I_{ON} \sim 23 \,\mu A/\mu m$ ). The expected enhancement is due to the lowering of both the source side tunneling width and the effective tunneling barrier in the case of the staggered-source TFET,<sup>8)</sup> while in the case of the  $\delta$ -doped TFET it is mainly due to the reduction in the tunneling width for the same tunneling barrier.<sup>6)</sup>

Figures 2(a) and 2(b) show the measured  $I_d$ – $V_g$  at 300, 150, and 77 K. RT leakage floors are elevated and the measured SS is higher than the 60 mV/dec thermal limit. However, both decrease significantly at low temperatures at a rate faster than the linear dependence of kT/q with respect to temperature *T*, with a minimum point value of 40 mV/dec at 77 K as shown in Figs. 2(c) and 2(d). The degradation

in SS at high temperatures is attributed to trap-assisted tunneling followed by thermionic emission via large midgap interface state density.<sup>11)</sup> Insets in Figs. 2(a) and 2(b) show the output characteristics at 77 K. Negative differential resistance (NDR) in the drain-to-source forward bias regime, at high  $V_{GS}$ , confirms the presence of a gated tunneling junction for both the fabricated devices.

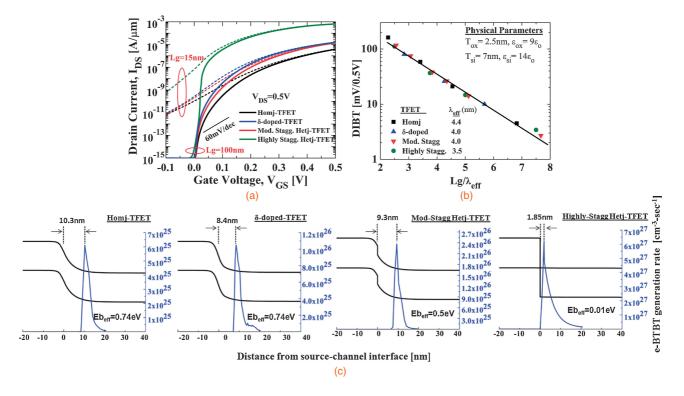

$I_{\rm ON}$  in our devices can be further improved by increasing the electrostatic gate control and by increasing the amount of stagger in the III-V Hetj-TFET.<sup>8,9)</sup> However, it is also important to identify whether these enhancement techniques lead to the improvement or degradation in TFET device scalability. To compare the device scalability numerically, we consider a UTB-DG structure with body  $(T_{SI})$  thickness of 7 nm, high-k gate dielectric thicknesses  $(T_{OX})$  of 2.5 nm and an effective EOT of 1 nm. We consider four TFET structures: (a) In<sub>0.53</sub>Ga<sub>0.47</sub>As Homj-TFET, (b) In<sub>0.53</sub>Ga<sub>0.47</sub>As  $\delta$ -doped-TFET, (c) moderately staggered GaAs<sub>0.5</sub>Sb<sub>0.5</sub>/  $In_{0.53}Ga_{0.47}As$  Hetj-TFET with effective  $E_b$  of 0.5 eV(similar to the one fabricated in this work), and (d) highly staggered lattice-matched  $GaAs_vSb_{1-v}/In_{1-x}Ga_xAs$  heterojunction with an effective  $E_b$  of 10 meV. Case (d) with an effective  $E_b$  of 10 meV can be realized with y = 0.1 and  $x = 0.0^{13}$  However, in order to account only for the effect of the increase in stagger on the scalability of TFET, bandgap and dielectric constants of source, channel and drain materials for case (d) were kept the same as those for the case (c). A dynamic non local band-to-band tunneling (BTBT) model was used to compute the tunneling current.<sup>12)</sup> Reduced tunneling mass and the change in bandgap due to thin-body quantization were obtained using Nextnano3 and included in the numerical simulations.<sup>13)</sup>

Fig. 3. (a) Simulated  $I_d$ – $V_g$  for UTB-DG Homj-TFET,  $\delta$ -doped TFET, moderately staggered Hetj-TFET and highly staggered Hetj-TFET for small and large channel lengths of 15 and 100 nm and  $V_{CC} = 0.5$  V. (b) DIBT plotted vs gate (channel) length ( $L_g$ ) normalized to  $\lambda_{eff}$  such that the DIBT values lie along one curve. Inset summarizes extracted  $\lambda_{eff}$ . (c) Electron BTBT generation rate profile plotted along the channel in the near turn-on regimes.

Figure 3(a) shows the simulated  $I_d - V_g$  for 15 nm (short) and 100 nm (long) gate (channel) length devices for the four TFET structures at a fixed supply voltage of 0.5 V. Figure 3(b) shows the drain-induced barrier thinning (DIBT) plotted as a function of the gate length which, in turn, is normalized to the respective effective electrostatic scaling length  $\lambda_{eff}$ .  $\lambda_{eff}$  for Homj-TFET was extracted from the exponential fit to the simulated potential profile along the channel.<sup>14,15)</sup> For the rest of the TFETs,  $\lambda_{eff}$  was obtained by scaling  $\lambda_{eff}$  for Homj-TFET such that DIBT values for each of them followed a single curve. The extracted  $\lambda_{eff}$  is summarized as an inset in Fig. 3(b). The difference in the scaling lengths for different TFET device architectures can be understood by analyzing the electron band-to-band generation (e-BTBT) rate within the channel in the near turn-on regime [Figs. 3(c) and 3(d)]. Clearly, with stagger and pocket doping, the channel side component of tunneling width  $(x_{ch})$  decreases bringing the peak in the generation rate closer to the source-channel junction. Since the electrostatic gate control is maximum near the source (away from the drain potential), the lower tunneling width in the channel leads to a lower  $\lambda_{eff}$  and, hence, higher device scalability. Highly staggered Hetj-TFET shows maximum scalability resulting from the lowest  $\lambda_{eff}$ .

In summary,  $I_{\rm ON}$  enhancements over n-channel In<sub>0.53</sub>-Ga<sub>0.47</sub>As Homj-TFET are experimentally demonstrated by utilizing i) a staggered GaAs<sub>0.5</sub>Sb<sub>0.5</sub> source and ii) an N+ pocket ( $\delta$ )-doped channel. Both techniques show 100% enhancement in drive current over Homj-TFET at  $V_{\rm DS} =$ 0.75 V and  $V_{\rm GS} = 2.0$  V, with the Hetj-TFET showing the maximum  $I_{\rm ON}$  of 60  $\mu$ A/ $\mu$ m at  $V_{\rm GS} = 2.5$  V. UTB-DG-TFET simulations were carried out to compare the scalability of staggered-source GaAs<sub>y</sub>Sb<sub>1-y</sub>/In<sub>1-x</sub>Ga<sub>x</sub>As Hetj-TFET with those of  $In_{0.53}Ga_{0.47}As$  Homj-TFET and  $\delta$ -doped-TFET. While  $\delta$ -doped TFET and moderately staggered Hetj-TFET show improved but similar scalability due to smaller tunneling width, highly staggered Hetj-TFET shows maximum scalability due to the lowest effective electrostatic scaling length resulting from the lowest tunneling width.

**Acknowledgments** This work was supported by the Nanoelectronics Research Initiative (NRI) through the Midwest Institute for Nanoelectronics Discovery (MIND). We thank Professor Thomas N. Jackson, Department of Electrical Engineering, Pennsylvania State University at University Park for the low-temperature plasma-enhanced atomic layer deposition of  $Al_2O_3$ .

- K. K. Bhuwalka, S. Sedlmaier, A. K. Ludsteck, C. Toksdorf, J. Schulz, and I. Eisele: IEEE Trans. Electron Devices 51 (2004) 279.

- W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu: IEEE Electron Device Lett. 28 (2007) 743.

- F. Mayer, C. Le Royer, J. Damlencourt, K. Romanjek, F. Andrieu, C. Tabone, B. Previtali, and S. Deleonibus: IEDM Tech. Dig., 2008, p. 163.

- S. Mookerjea, D. Mohata, R. Krishnan, J. Singh, A. Vallett, A. Ali, T. Mayer, V. Narayanan, D. Schlom, A. Liu, and S. Datta: IEDM Tech. Dig., 2009, p. 949.

- H. Zhao, Y. Chen, Y. Wang, F. Zhou, F. Xue, and J. Lee: IEEE Electron Device Lett. 31 (2010) 1392.

- N. Venkatagirish, R. Jhaveri, and J. C. S. Woo: IEEE Trans. Electron Devices 55 (2008) 1013.

- 7) T. Krishnamohan, K. Donghyun, S. Raghunathan, and K. Saraswat: IEDM Tech. Dig., 2008, p. 947.

- A. S. Verhulst, W. G. Vandenberghe, K. Maex, and G. Groeseneken: J. Appl. Phys. **104** (2008) 064514.

- 9) Y. Lu, A. Seabaugh, P. Fay, S. J. Koester, S. E. Laux, W. Haensch, and S. O. Koswatta: 68th Device Research Conf. Dig., 2010, p. 17.

- D. A. Mourey, D. A. Zhao, S. Jie, and T. N. Jackson: IEEE Trans. Electron Devices 57 (2010) 530.

- S. Mookerjea, D. Mohata, T. Mayer, V. Narayanan, and S. Datta: IEEE Electron Device Lett. 31 (2010) 564.

- 12) Sentaurus Users Guide, Ver. C-2009.06.

- 13) http://www.nextnano.de/nextnano3/

- 14) L. Liu and S. Datta: 68th Device Research Conf. Dig., 2010, p. 15.

- 15) L. Xiaoping and T. Yuan: IEEE Trans. Electron Devices 51 (2004) 1385.