## Impact of Interface States on Sub-threshold Response of III-V MOSFETs, MOS HEMTs and Tunnel FETs

W.C. Kao, E. Hwang, S. Mookerjea and S. Datta <sup>1</sup>The Pennsylvania State University, University Park, PA 16802, USA Phone: (814) 865 2063, Fax: (814) 865 7065, E-mail: <u>wxk151@psu.edu</u>

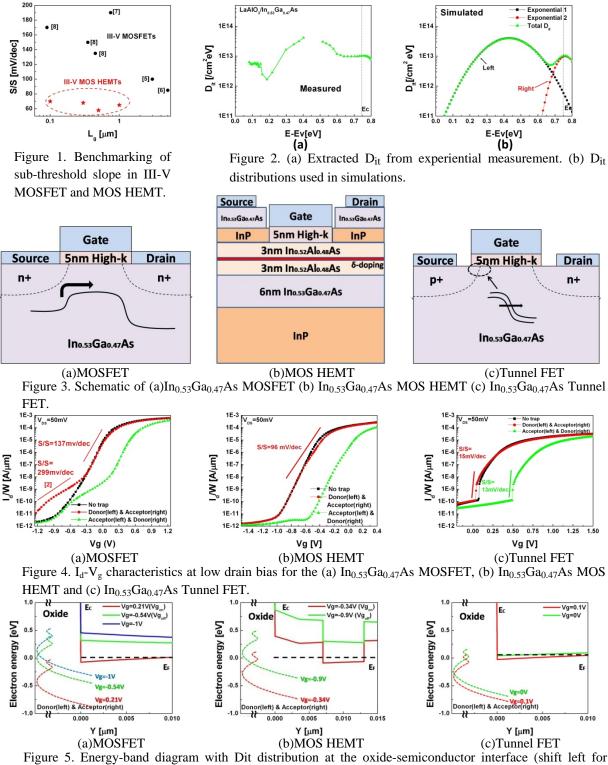

Logic transistor scaling following Moore's Law over the last four decades has resulted in unprecedented increase in logic performance. However, rising transistor count has also led to increased energy consumption in modern VLSI. Thus, high mobility channel transistors (such as III-V) [1,2] and steep subthreshold slope transistors [3] are needed in future to aggressively scale the supply voltage (Vcc) for logic transistors. High mobility quantum well FETs (QWFETs) (e.g.  $In_{0.7}Ga_{0.3}As$  and InSb) have already been demonstrated at 0.5V Vcc with high performance [1,2], albeit with high gate leakage due to the Schottky gate. Efforts are underway to integrate a high quality high-k dielectric with III-V transistors. Recently, inversion mode In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and MBD LaAlO<sub>3</sub> oxides as well as insulated gate InGaAs MOS HEMT devices have been demonstrated[4,5]. Fig. 1 shows the benchmarking of the subthreshold slope values in InGaAs based MOSFETs and MOS HEMTs with the former typically showing higher values than the latter [9]. In this work, we present a drift-diffusion based numerical simulation and analysis of the influence of interface states (D<sub>it</sub>) present at the high-k dielectric and InGaAs interface on the sub-threshold response of 3 different types of transistor architecture: MOSFETs, MOS HEMTs and Tunnel FETs. Fig. 2(a) shows the experimentally measured  $D_{it}$  profile at the interface of an in-situ deposited LaAlO<sub>3</sub> high-k dielectric and In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. For simulation purpose, we approximate the D<sub>it</sub> profile by a superposition of two exponential trap distributions (Fig. 2(b)) – the left distribution spanning across a large portion of the bandgap (left) and the right distribution extending into the conduction band. Figs. 3(a), (b) and (c) show the crosssection schematics of 3 different transistor architectures – an inversion mode surface channel  $In_{0.53}Ga_{0.47}As$ MOSFET, an accumulation mode buried channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSHEMT with InAlAs barrier layer and an  $In_{0.53}Ga_{0.47}As$ -based interband tunnel FET. Figs. 4 (a)-(c) show the simulated transfer characteristics of the 3 devices along with their respective energy band diagrams and Fermi level movement as the devices turn on (Figs. 5 (a)-(c)). In MOSFETs, we identify 2 different regions for sub-threshold response: in the first region (-1V < Vg < -0.54 V), the Fermi level,  $E_F$ , sweeps the entire left distribution and causes severe degradation in sub-threshold slope (300 mV/dec), while in the second region E<sub>F</sub> spans one half of the right distribution up to its peak and the slope improves to 137 mV/dec for a total E<sub>F</sub>movement of 0.53V to turn the device on (Fig. 4(a)). It is to be noted that, since the second distribution extending into the conduction band has lower peak value, a high inversion charge and thereby a high on-current is expected in InGaAs MOSFETs, despite its poor sub-threshold slope. The donor and the acceptor character of the  $D_{it}$  also affects the threshold voltage,  $V_T$ , of the MOSFET with the latter causing a positive  $V_T$  shift. In MOS HEMTs, the sub-threshold slope is less affected by D<sub>it</sub> than MOSFETs since the Fermi level moves by 0.4V through the first peak and does not even reach the second peak when the quantum well turns on (Fig. 5(b)). Finally, in the case of InGaAs TFETs, the Fermi level moves by a very little amount to turn the device on. Tunnel FETs turn on abruptly when the valence band edge in the p+ source region is raised above the conduction band edge in the channel which is already weakly inverted in the off-state, this gives rise to steep  $(\langle kT/q \rangle)$  sub-threshold slope. Fig, 5(c) shows that, even in the presence of interface states, the steep sub-threshold behavior is retained since the Fermi level sweeps the interface by only a small amount (~ 40mV) and primarily across the second D<sub>it</sub> distribution which has lower peak density. In this work, we have shown how the same exact D<sub>it</sub> distribution at the high-k/III-V interface can affect the sub-threshold response of different transistor architecture in dramatically different ways.

**References:** [1] S. Datta, G. Dewey et al, Electron Device Letters, vol. 28, pp. 685 (2007) [2] S. Datta, T. Ashley et al, International Electron Devices Meeting (IEDM) Technical Digest, pp. 763-766 (2005) [3] S. Mookerjea, S. Datta, Proc DRC pp.

47 (2008) [4] R. Hill et al. Elec. Letters, vol 44, pp. 498-(2008) [5] S. Koveshnikov, Proc. DRC (2008) [6] H. Zhao et al, Appl Phys. Lett, 92, 253506 (2008) [7] Y. Xuan et al., Proc. IEDM, pp 371 (2008) [8] Y. Sun, Proc. IEDM, pp 367 (2008) [9] R. Hill et al , Proc. DRC, pp 251 (2009)

Figure 5. Energy-band diagram with Dit distribution at the oxide-semiconductor interface (shift left for clarity) for (a)  $In_{0.53}Ga_{0.47}As$  MOSFET, (b)  $In_{0.53}Ga_{0.47}As$  MOS HEMT and (c)  $In_{0.53}Ga_{0.47}As$  Tunnel FET at different gate voltage. Here  $V_{on}$  is  $V_g$  when  $E_F-E_C=3kT$ .