# Modeling and Simulation of Vanadium dioxide Relaxation Oscillators

Paolo Maffezzoni, Senior Member, IEEE, Luca Daniel, Member, IEEE, Nikhil Shukla, Student Member, IEEE, Suman Datta, Fellow, IEEE, Arijit Raychowdhury, Senior Member, IEEE

*Abstract*— This paper deals with modeling and simulation of a new family of two-terminal devices fabricated with vanadium dioxide material. Such devices allow realization of very compact relaxation nano-oscillators that can be connected electronically to form arrays of coupled oscillators. Challenging applications of oscillator arrays include the realization of multi-phase signal generators and massively parallel brain-inspired neurocomputing. In the paper, a circuit-level model of the vanadium dioxide device is provided which enables extensive electrical simulations of oscillator systems built on the device. The proposed model is exploited to explain the dynamics of vanadium dioxide relaxation oscillators as well as to accomplish a robust parameter design. Applications to the realization of voltage-controlled oscillators and of multi-phase oscillator arrays are illustrated.

#### I. INTRODUCTION

Electronic oscillators have always played a unique role in the implementation of fundamental tasks such as clock generation, timing synchronization, and frequency synthesis. In the last few years, a great research effort has been spent in developing new fabrication processes, alternative to conventional CMOS, and targeted at the realization of compact and easy scalable nano-oscillators [1]–[3]. Such emerging technologies are expected to soon allow the large-scale integration of array of coupled oscillators paving the way to novel applications. Relevant applications are envisaged in the area of multiphase oscillations for frequency synthesis and clock distribution [4]-[5], noise-mitigation techniques [6] as well as in visionary brain-inspired parallel computing for data analysis and pattern recognition [7]–[12].

Among all emerging fabrication technologies, the one based on Vanadium dioxide (VO<sub>2</sub>) material is now attracting great interest due to the relative simplicity of the process flow with the possibility to control and couple the devices electronically. It has recently been proved that compact relaxation oscillators can be obtained by connecting a VO<sub>2</sub> two-terminal device with an electrical resistor and a capacitor. Discrete-component implementations of these VO<sub>2</sub>-based oscillators have been realized in the laboratory [11]. First attempts to couple and

P. Maffezzoni is with the Politecnico di Milano, Milan, Italy.

synchronize more VO<sub>2</sub> oscillators are currently under investigation [1], [13]. However, similarly to what has been done for MOSFET devices, as the VO<sub>2</sub>-based manufacturing process gets more mature, it becomes more apparent the need for developing circuit-level models of the new physical devices. Such models are in fact needed to study the dynamics of relaxation oscillators built on VO<sub>2</sub> devices as well as to asses a design methodology which should be robust against the variability of the fabrication process. Circuit-level models are also key to simulate and control synchronization in array of VO<sub>2</sub> oscillators coupled through linear (e.g. resistor) or nonlinear electrical devices (e.g. transistors).

The main electronic features of  $VO_2$  devices are: a) A switching-like behavior with large and abrupt change in electrical conductivity that can be triggered by the applied electrical voltage. Physically this corresponds to abrupt but not instantaneous insulator-to-metal and metal-to-insulator phase transitions induced by the application of critical electric fields [16]. b) The presence of a hysteresis in the device characteristic with the insulator-to-metal transition (IMT) and the metal-to-insulator transition (MIT) being driven by two different critical electric field values.

## A. Our contributions

This paper provides the following contributions:

- 1) We describe a *driving point* equivalent model for a  $VO_2$  two-terminal device which is able to accurately reproduce its hysteretic behavior. The model is implemented through continuous relationships that enhance the robustness of the numerical simulations.

- 2) Extensive simulations of a single  $VO_2$ -based oscillator are leveraged to investigate its qualitative dynamic behavior and to find the conditions for which stable oscillations occur.

- 3) In view of this understanding, the constraints that circuit parameters have to satisfy to ensure oscillation and the expression of the resulting oscillating frequency are derived in closed form. It is shown how circuit parameters can be selected within their admissible domains so as to enhance the design robustness against VO<sub>2</sub> process variability.

- We present some interesting applications in the realization of voltage-controlled oscillators and of multi-phase oscillator arrays.

L. Daniel is with the Massachusetts Institute of Technology, Cambridge, MA, USA.

N. Shukla, S. Datta are with the Pennsylvania State University, University Park, PA, USA.

A. Raychowdhury is with the Georgia Institute of Technology, Atlanta, GA, USA.

Copyright (c) 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending an email to pubs-permissions@ieee.org.

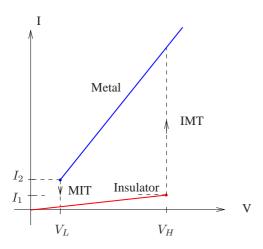

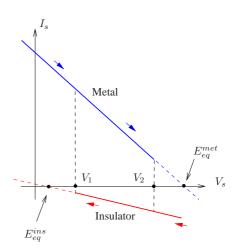

Fig. 1. *I-V* characteristic of a VO<sub>2</sub> device.

#### B. Paper organization

This paper is divided in the following sections. In Sec. II, we describe the I-V characteristic of a VO<sub>2</sub> device and we introduce its circuit-level model. In Sec. III, we use simulations to investigate the dynamic of the oscillating mechanism. In Sec. IV, we find the closed-form constraints on circuit parameters that ensure oscillation. Finally, in Sec. V we illustrate applications.

# II. CIRCUIT-LEVEL MODEL OF A $VO_2$ DEVICE

Vanadium dioxide (VO<sub>2</sub>) is a correlated electron material that exhibits insulator-to-metal and metal-to-insulator phase transitions commonly occurring just above room temperature. The exact physics driving such transitions is still debated with some authors proposing thermal mechanisms [14] [15] and some others proposing electrical ones [16]. Independently of the underlying physical mechanism, it has been shown that such transitions can be triggered using various external stimuli including thermal [17], electrical [18], as well as optical and mechanical. Being interested in electronic applications, in this paper we will focus on the electrically-triggered  $VO_2$ switching-like behavior [19], [20]. The typical qualitative shape of the electronic I-V current-voltage characteristic of a two-terminal VO<sub>2</sub>, measured at a given environment temperature, is reported in Fig. 1<sup>-1</sup>. For relatively low currents, the device has an insulator-like behavior with  $V = I \cdot R_{ins}$ , where  $R_{ins}$  is the resistance in the insulator state. When the device current approaches the critical value  $I_1$ , corresponding to the voltage level  $V_H = I_1 \cdot R_{ins}$ , an IMT occurs and the current I abruptly increases. This transition is abrupt but not instantaneous with a finite intrinsic electronic switching time [21]. In the metallic state, we have that  $V = I \cdot R_{met}$  with a much smaller resistance  $R_{met} \ll R_{ins}$ . In this condition, to bring the device back to the insulator state, the current should be reduced under the critical value  $I_2$ , corresponding to the low voltage level  $V_L = I_2 \cdot R_{met} < V_H$ , at which the inverse MIT occurs.

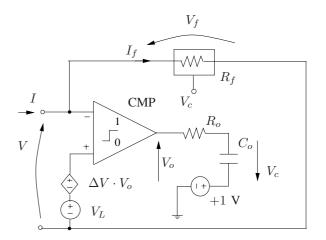

Fig. 2. Driving-point equivalent model of a VO2 device where  $\Delta V = V_H - V_L.$

TABLE I CIRCUIT VARIABLES IN INSULATOR AND METAL STATES

| State     | $V_o$ | $V_c$ | $V^+$ | $G_f$     |

|-----------|-------|-------|-------|-----------|

| Insulator | 1 V   | 0 V   | $V_H$ | $G_{min}$ |

| Metal     | 0 V   | 1 V   | $V_L$ | $G_{Max}$ |

To model this hysteretic behavior, we adopt the *driving point* equivalent circuit [22]–[24] with abrupt (but not instantaneous) transitions described in Fig. 2. Excellent dissertations on how to model hysteresis in electronic circuits can also be found in [25]–[28]. In our model, the *state* (i.e., insulator or metal) of the device is decided by a voltage comparator (CMP) and it is stored into the intrinsic capacitor  $C_o$ . The value of the product  $\tau_o = R_o \times C_o$  is selected so as to reproduce the time constant of the phase transition detected in laboratory measurements. For the comparator, we adopt the following input-output relationship

$$V_o = 0.5 \cdot (1 + \tanh(2\,\alpha\,V_{in})),\tag{1}$$

where  $V_{in} = V^+ - V^-$  and  $V_o$  are the input and output voltages, respectively, while  $\alpha$  is the parameter that determines the slope of the transition curve. The comparator output voltage  $V_o$ , whose value ranges from 0 to 1 V, is transferred by a voltage-controlled voltage source of gain  $\Delta V = V_H - V_L$ at the comparator input terminal +. In this way, the voltage  $V^+$  takes one among the two critical levels  $V_L$  and  $V_H$  for  $V_o = 0$  and  $V_o = 1$ , respectively. The device current is given by the current  $I = I_f = G_f V_f$  that flows into the feedback resistor  $R_f$  shown in Fig. 2. The electrical conductance of such a resistor is controlled by the state voltage  $V_c$  as follows:

$$G_f = G_{min} (1 - V_c) + G_{Max} V_c,$$

(2)

where  $G_{min} = 1/R_{ins}$  and  $G_{Max} = 1/R_{met} >> G_{min}$  are the device conductance in the insulator and metal state, respectively. The values that the circuit variables assume in the two states are summarized in Tab. I.

In the insulator state, the CMP output is  $V_o = 1$  V and  $V_c = 0$  (at DC regime). In this state,  $V^+ = V_H$  and  $G_f =$

<sup>&</sup>lt;sup>1</sup>The *I*-V characteristics are experimentally observed to be central symmetric with regard to the origin of coordinates, however in our applications we will focus on the case V > 0.

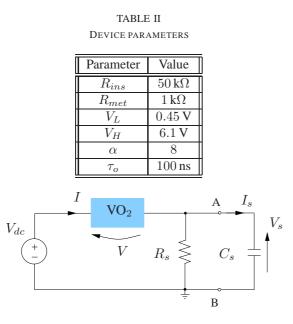

Fig. 3. The circuit of the relaxation oscillator.

$G_{min}$ . Hence, if V is gradually increased until it approaches  $V_H$ , it initiates an IMT. Observing that  $V_{in} = -V + V_H$ ,  $V_c = 1 - V_o$  (at DC) and in view of (1), the *I*-V relationship for values of V close to  $V_H$  becomes

$$I = 0.5 (G_{Max} + G_{min}) \cdot V + 0.5 (G_{Max} - G_{min}) \cdot V \cdot \tanh(2 \alpha (V - V_H)).$$

(3)

After the device has completed its transition to the metallic state, the CMP output becomes  $V_o = 0$  V and  $V_c = 1$ . In this state,  $G_f = G_{Max}$  and  $V^+ = V_L$ . Thus, it is only when V is reduced below  $V^+ = V_L$  that a reverse MIT can occur completing the cycle of the hysteresis characteristic.

The parameters of the proposed VO<sub>2</sub>-device model are summarized in Tab. II along with the values they assume for a  $2 \mu$ m-length VO<sub>2</sub> device. These parameters were extracted in the laboratory by fitting the experimental curve of the device. After being tuned with the experimental data of a given VO<sub>2</sub> device, the proposed circuit-level model is able to realistically reproduce its electronic behavior seen at the external terminals. In addition, the continuous dependence of the electrical conductance (2) on the internal state variable  $V_c(t)$  and the existence of the continuous *I-V* relation (3) near the transitions, give the model those regularity properties that are needed for robust numerical simulations.

#### **III. RELAXATION OSCILLATION MECHANISM**

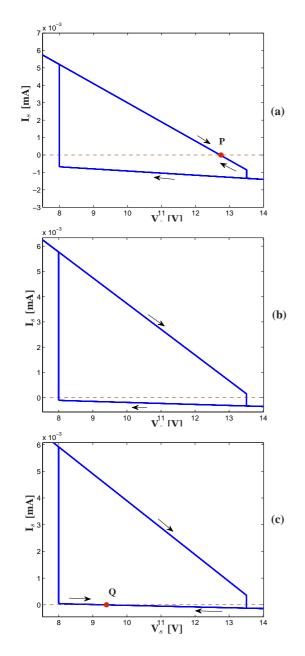

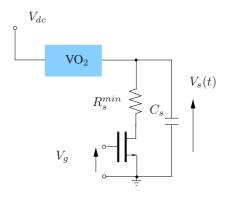

In this section, the proposed device model is leveraged to investigate the dynamics of the VO<sub>2</sub>-based relaxation oscillator shown in Fig. 3. The circuit is obtained by connecting the VO<sub>2</sub> device to an external resistor  $R_s$  and capacitor  $C_s$  and it is supplied by a DC voltage source  $V_{dc}$ . In this section, we make extensive use of numerical simulation to determine the static  $I_s$ - $V_s$  characteristic seen by the external capacitor  $C_s$  at its terminals A-B. In doing that we assume the VO<sub>2</sub>device parameters values in Tab. II and  $V_{dc} = 14$  V while we take  $R_s$  as a varying parameter. The  $I_s$ - $V_s$  characteristic is thus computed by replacing the capacitor  $C_s$  by a DC voltage source of sweeping value and performing repeated DC simulations. Such characteristics exhibit hysteresis being formed of two different sloping straight lines (i.e., branches) connected by sharp vertical transitions as plotted in Fig. 4 for the three cases: a)  $R_s = 10 \text{ k}\Omega$ , b)  $R_s = 40 \text{ k}\Omega$  and c)  $R_s = 80 \text{ k}\Omega$ .

We then exploit a simplification suggested by experimental evidences. In fact, measurements show that the time constant  $\tau_o$  associated to VO<sub>2</sub> phase transitions is several orders of magnitude shorter compared to the typical time constants governing relaxation oscillation dynamics [21]. Oscillation dynamics can thus be investigated by considering the internal capacitor  $C_o$  as an open circuit and using the aforementioned static  $I_s$ - $V_s$  characteristic along with the  $C_s$  capacitor branch equation

$$V_s(t) = I_s(t)/C_s.$$

(4)

In the case of Fig. 4a), starting from  $V_s(t_0) \approx 0$  V, a positive current  $I_s(t)$  charges the capacitor making  $V_s(t)$  to grow in time. The growth of  $V_s(t)$  stops for  $V_s(t) \approx 12.7$  V where the characteristic intersects the zero current axis at point P. In fact, for greater  $V_s(t)$  values the sign of  $I_s(t)$  becomes negative and the direction of the dynamic flow reverses meaning that the equilibrium point P is *stable*. As a consequence, in case a), the circuit in Fig. 3 will reach a DC regime and no oscillation will appear.

A completely different dynamic behavior is predicted from Fig. 4b). In this case, before intersecting the equilibrium condition  $I_s = 0$ , the upper branch of the characteristic undergoes a sudden vertical transition (which corresponds to a MIT of the VO<sub>2</sub> device) towards the lower branch where  $I_s(t) < 0$  A and where  $V_s(t)$  can only decrease in time. However, before intersecting the equilibrium condition  $I_s = 0$ the lower branch characteristic undergoes a new transition (which corresponds to a IMT of the  $VO_2$  device) to the upper branch. In case b), a limit cycle arises and the circuit in Fig. 3 will sustain a relaxation oscillation. Finally, in case c) for a much greater  $R_s$ , a new stable equilibrium point Q arises from the intersection of the lower branch of the characteristic with the equilibrium condition and therefore the circuit cannot oscillate anymore. We thus conclude that the circuit in Fig. 3 will actually oscillate only if the  $I_s$ - $V_s$  characteristic seen at the terminals of the external capacitor has the qualitative shape shown in Fig. 4(b).

## IV. ANALYSIS THROUGH CLOSED-FORM EXPRESSIONS

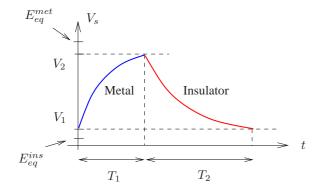

This qualitative characteristic is redrawn in Fig. 5 along with the important information that will be used in our analysis. The upper straight line in Fig. 5 corresponds to the  $VO_2$  device being in the metal state while the lower one corresponds to the device being in the insulator state.

From the circuit in Fig. 3, it is seen that in either metal or insulator state the characteristic is analytically described by the equivalent Thevenin model

$$V_s = I_s R_{eq} + E_{eq}.$$

(5)

Fig. 4.  $I_s$ - $V_s$  characteristics: a)  $R_s = 10 \,\mathrm{k\Omega}$ , b)  $R_s = 40 \,\mathrm{k\Omega}$  and c)  $R_s = 80 \,\mathrm{k\Omega}$ . The arrows indicate the dynamic flow, i.e. the direction of the working-point evolution in time.

In the metal state, the model parameters in (5) are given by

$$R_{eq}^{met} = \frac{R_{met} \cdot R_s}{R_{met} + R_s},$$

$$E_{eq}^{met} = V_{dc} \cdot \frac{R_s}{R_{met} + R_s},$$

(6)

whereas they take the values

$$R_{eq}^{ins} = \frac{R_{ins} \cdot R_s}{R_{ins} + R_s},$$

$$E_{eq}^{ins} = V_{dc} \cdot \frac{R_s}{R_{ins} + R_s}$$

(7)

in the insulator state. Observing from Fig. 3 that  $V_s = V_{dc} - V$ ,

Fig. 5. Qualitative shape of the  $I_s\mathcase-V_s$  characteristic seen by the external capacitor  $C_s.$

we have that phase transitions occur when  $V_s$  takes the values

$$V_1 = V_{dc} - V_H,$$

$$V_2 = V_{dc} - V_L,$$

(8)

for IMT and MIT, respectively. Thus, for the existence of oscillation the following constraints

$$V_1 > E_{eq}^{ins},\tag{9a}$$

$$V_2 < E_{eq}^{met} \tag{9b}$$

should hold.

From (9a), along with (8) and (7), we deduce the  $R_s$  upper bound

$$R_s < R_s^{max} = R_{ins} \cdot \frac{V_{dc} - V_H}{V_H}.$$

(10)

Similarly, from (9b), with (8) and (7), we derive the  $R_s$  lower bound

$$R_s > R_s^{min} = R_{met} \cdot \frac{V_{dc} - V_L}{V_L}.$$

(11)

Relaxation oscillation only occurs if the series resistance  $R_s$  is chosen within the *admissible interval*  $(R_s^{min}, R_s^{max})$  defined by (11) and (10). Thus, forcing the existence condition  $R_s^{max} > R_s^{min}$ , we obtain a lower bound for the voltage supply value

$$V_{dc} > V_{dc}^{min} = \frac{R_{ins} - R_{met}}{R_{ins}/V_H - R_{met}/V_L}.$$

(12)

The width of the admissible interval grows for increasing values of  $V_{dc}$  with the width being zero for  $V_{dc} = V_{dc}^{min}$ . As a consequence, a safe design strategy can consist in the following steps:

- 1) fix  $V_{dc} \approx (1.5 \div 2) \cdot V_{dc}^{min}$

- 2) determine  $R_s^{min}$  with (11)

- 3) determine  $R_s^{max}$  with (10)

Fig. 6. Waveform  $V_s(t)$  at the output of the relaxation oscillation.

4) choose

$$R_s = (R_s^{min} + R_s^{max})/2.$$

The assumption of  $V_{dc}$  sufficiently larger than  $V_{dc}^{min}$  combined with the selection of  $R_s$  in the middle of its admissible interval helps enhancing the robustness of oscillation against the variability of VO<sub>2</sub>-device parameters.

We end this section by providing a closed-form estimation for the period T of relaxation oscillation. Without loss of generality we can assume that one oscillating period  $T = T_1 + T_2$ is formed of one time interval  $T_1$  where the VO<sub>2</sub> device is in the metal state followed by a time interval  $T_2$  where the device is in the insulator state as plotted in Fig. 6. For  $0 \le t \le T_1$ , the analytical expression

$$V_{s}(t) = V_{s}^{met}(t) = \left(V_{1} - E_{eq}^{met}\right) \cdot \exp[-t/\tau_{met}] + E_{eq}^{met},$$

(13)

holds, where  $\tau_{met} = R_{eq}^{met} C_s$  is the time constant associated to metal state. While for  $T_1 \leq t \leq T_2$ ,  $V_s(t)$  has the analytical expression

$$V_s(t) = V_s^{ins}(t) = (V_2 - E_{eq}^{ins}) \cdot \exp[-(t - T_1)/\tau_{ins}) + E_{eq}^{met},$$

(14)

where  $\tau_{ins} = R_{eq}^{ins} C_s$  is the time constant in the insulator state.

Hence, by imposing  $V_s^{met}(T_1) = V_2$  and  $V_s^{ins}(T_1 + T_2) = V_1$ , we find the expressions of  $T_1$  and  $T_2$  respectively, and finally the period of oscillation

$$T = \tau_{met} \cdot \log_e \left( \frac{E_{eq}^{met} - V_1}{E_{eq}^{met} - V_2} \right) + \tau_{ins} \cdot \log_e \left( \frac{E_{eq}^{ins} - V_2}{E_{eq}^{ins} - V_1} \right).$$

(15)

The period thus depends on the parameters of the  $VO_2$  device as well as on the external electrical resistor and capacitor.

#### V. APPLICATIONS AND NUMERICAL RESULTS

In this section, we present three applications of the proposed modeling and simulation method.

## A. Robust design of a single VO<sub>2</sub>-based oscillator

We apply here the robust design strategy described in Sec. IV, steps from 1) to 4), to a relaxation oscillator built on the VO<sub>2</sub> device with the parameters reported in Tab. II and connected to the external capacitance  $C_s = 300$  pF. From (12),

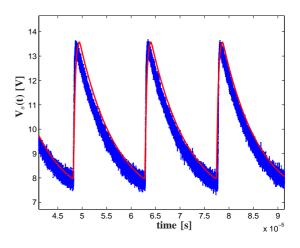

Fig. 7. Simulated (solid line) and measured (noisy oscillogram)  $V_s(t)$  waveforms for  $R_s=47\,{\rm k}\Omega.$

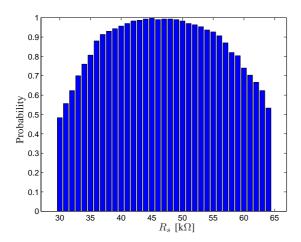

we find  $V_{dc}^{min} = 8.2$  V and thus, according to step 1), we select  $V_{dc} = 14$  V. Then, using (11) and (10), we get  $R_s^{min} = 30 \text{ k}\Omega$ and  $R_s^{max} = 64 \,\mathrm{k}\Omega$  and thus, according to step 4), we select  $R_s = 47 \,\mathrm{k}\Omega$ . Fig. 7 shows the steady state response  $V_s(t)$ simulated with the device model illustrated in Sec. II and that obtained with direct laboratory measurements: simulated and measured waveforms match with excellent accuracy and yield a relaxation oscillation at  $\approx 68$  kHz. This example shows how the proposed model, after being tuned with experimental data, is able to realistically reproduce the behavior of the circuits built on VO<sub>2</sub> devices. We check the robustness of oscillator design against possible variations of device resistances  $R_{ins}$  and  $R_{met}$  due to fabrication uncertainty. To this aim we assume that  $R_{ins} = R_{ins}^0 + \sigma_{ins} \cdot \mathcal{N}(0,1)$  and  $R_{met} = R_{met}^0 + \sigma_{met} \cdot \mathcal{N}(0, 1)$ , where  $R_{ins}^0 = 50 \,\mathrm{k}\Omega$  and  $R_{met}^0 = 1 \,\mathrm{k}\Omega$  are the resistances nominal value, whereas  $\mathcal{N}(0,1)$  denotes the unit normal distribution and  $\sigma_{ins}=5\,\mathrm{k}\Omega$ and  $\sigma_{met} = 0.2 \,\mathrm{k}\Omega$  are the standard deviations for insulator and metal resistances, respectively. We select 25 values of the series resistance  $R_s$  within the admissible interval of boundaries  $R_s^{min} = 30 \,\mathrm{k}\Omega$  and  $R_s^{max} = 64 \,\mathrm{k}\Omega$ . Hence, for each resistance value  $R_s$ , we perform a Monte Carlo simulation with randomly generated  $R_{ins}$  and  $R_{met}$  parameters and evaluate the probability for the VO<sub>2</sub>-based oscillator to oscillate (given by the ratio of the number of realizations that give an oscillating circuit on the total number of realizations). Fig. 8 reports the simulated oscillation probability versus the series resistance value: it clearly appears how for  $R_s$  close to  $47 \,\mathrm{k}\Omega$  the probability is almost 1 while it significantly reduces for  $R_S$  values near the admissible interval extremes.

## B. Voltage-controlled oscillator (VCO)

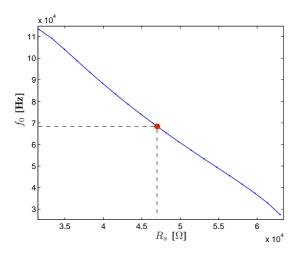

With the relaxation oscillator described in the previous subsection, we investigate the relationship between the oscillating frequency  $f_0 = 1/T$  and the value of  $R_s$  considered here as a free parameter ranging in its admissible domain. From (15), we find the relationship plotted in Fig. 9, which shows how oscillating frequency depends almost linearly on the resistance

Fig. 8. Oscillation probability versus series resistance

Fig. 9. Oscillating frequency versus resistance  $R_s$ . The big dot corresponds to the design centering of  $R_s$  in its admissible interval.

value. This result suggests that a straightforward way to realize a voltage-controlled oscillator is to use a variable series resistor whose resistance  $R_s$  can be controlled externally. A viable implementation is shown in Fig. 10: a resistor of fixed value  $R_s^{min}$  is series connected to the drain-source terminals of a MOS transistor. The drain-source  $R_{DS}(V_g)$  resistance of the transistor is controlled by its gate voltage  $V_g$  and contributes to determine the total series resistance  $R_s = R_s^{min} + R_{DS}(V_g)$ .

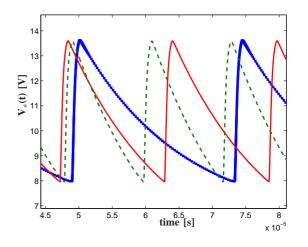

In simulations a realistic Spice model is adopted for the MOS transistor with transconductance parameter  $k_n = 120 \,\mu\text{A/V}^2$  and zero-bias threshold voltage  $V_{th_0} = 0.5 \text{ V}$ [29]. Fig. 11 shows the simulated VCO steady-state responses for three different controlling voltage values:  $V_g = 2.1 \text{ V}$ ,  $V_g = 2.3 \text{ V}$ ,  $V_g = 2.5 \text{ V}$ . The resulting oscillating frequencies, i.e.  $f_0 = 41 \text{ kHz}$ ,  $f_0 = 63 \text{ kHz}$  and  $f_0 = 85 \text{ kHz}$ , respectively, show how the proposed design, for the considered frequency range, is able to keep an almost linear relationship between oscillating frequency and controlling voltage  $V_g$ .

Fig. 10. VCO realization with a MOS transistor.

Fig. 11. Steady-state responses of the VCO for three values of  $V_g$ :  $V_g = 2.1$  V (squared marker);  $V_g = 2.3$  V (continuous line);  $V_g = 2.5$  V (dashed line).

#### C. Synchronization in coupled oscillators

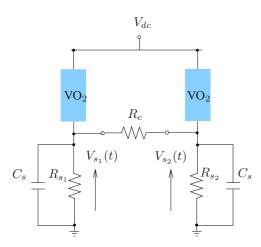

In this subsection, we investigate synchronization in some systems of coupled VO<sub>2</sub> relaxation oscillators. Synchronization mechanism in relaxation oscillators can be much more complex and multifaceted than that of harmonic oscillators previously investigated in the literature [30]–[33]. We start with the elementary array shown in Fig. 12 made of two oscillators coupled through a resistor  $R_c$  whose conductance  $1/R_c$  determines the *strength of coupling*.

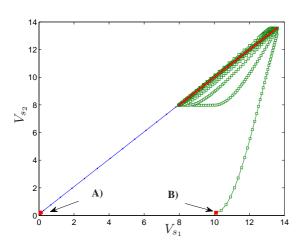

We first consider the *ideal case* of two perfectly identical oscillators with  $R_{s_1} = R_{s_2} = 47 \,\mathrm{k\Omega}$ . We fix  $R_c = 100 \,\mathrm{k\Omega}$  which corresponds to a relatively weak coupling scenario. In this case, simulations show that the two oscillators synchronize in frequency with perfectly aligned phase, i.e. they achieve perfect *in-phase synchronization* irrespectively of the initial conditions. Fig. 13 reports the trajectories of the oscillators responses in the variable space  $(V_{s_1}, V_{s_2})$  for two different initial conditions: A)  $V_{s_1}(0) = V_{s_2}(0) = 0 \,\mathrm{V}$ , corresponding to both oscillators in the insulator states; B)  $V_{s_1}(0) = 10 \,\mathrm{V}$  and  $V_{s_2}(0) = 0 \,\mathrm{V}$  with the first oscillator in the metal state and the second oscillator in the insulator state. In both cases A) and B), asymptotically for  $t \to \infty$ , the output responses superimpose, i.e.  $V_{s_1}(t) = V_{s_2}(t)$ , describing a straight segment in the variable space  $(V_{s_1}, V_{s_2})$ .

Fig. 12. Two relaxation oscillators coupled through the resistor  $R_c$ .

Fig. 13. Trajectories of two weakly coupled identical oscillators starting from different initial conditions A) and B).

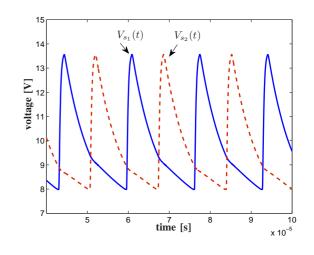

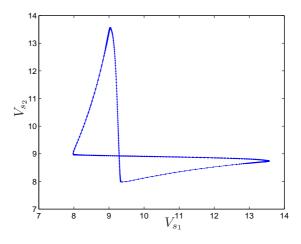

The hypothesis of perfectly identical oscillators is never satisfied in real implementations where small mismatches between the oscillators are unavoidable due to circuit parameters variability. Mutual synchronization greatly depends on the matching of oscillating frequencies of the two oscillators when working uncoupled. In turn these frequencies depend on the series resistances. To investigate the effect of parameter variability, we assume a 1% mismatch in the values of the series resistances, i.e.  $R_{s_1} = 47 \text{ k}\Omega$ ,  $R_{s_2} = 46.5 \text{ k}\Omega$ . Fig. 14 shows the steady-state responses of the mismatched oscillators in the case of weak coupling  $R_c = 100 \,\mathrm{k}\Omega$ : the two oscillators still synchronize in frequency, however, in this case, their phases are not aligned anymore. Besides, the common oscillating frequency reduces to 60 kHz. Fig. 15 shows the asymptotic trajectory described by the mismatched oscillators responses for  $t \to \infty$ . This trajectory corresponds to the projection of the limit cycle onto the  $(V_{s_1}, V_{s_2})$  subspace.<sup>2</sup>

Simulations reveal that the responses of the mismatched os-

Fig. 14. Responses of oscillators with small mismatch, i.e.  $R_{s_1} = 47 \text{ k}\Omega$  and  $R_{s_2} = 46.5 \text{ k}\Omega$ , and weak coupling  $R_c = 100 \text{ k}\Omega$ .

Fig. 15. Asymptotic trajectory described by the two weakly coupled mismatched oscillators.

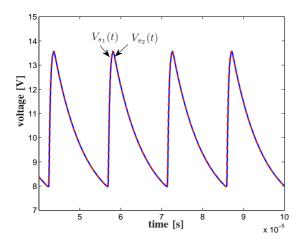

cillators can still be realigned in phase by gradually increasing the coupling strength. Fig. 16 shows the phase aligned (with a residual phase misalignment  $< 1^{\circ}$ ) responses achieved for the coupling strength  $R_c = 20 \text{ k}\Omega$ .

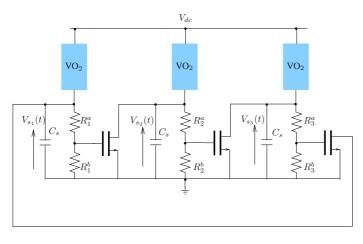

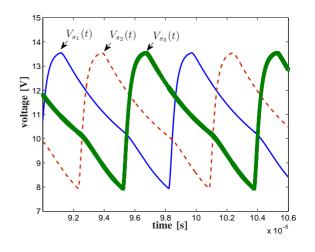

As a final example, we study synchronization in the closedin-feedback chain array shown in Fig. 17 where mutual coupling is realized through MOS transistors. Coupling strength can be controlled by varying the W/L aspect ratio of the coupling transistors. For harmonic oscillators, phase synchronization in chain arrays have been recently investigated in [33] using phase-domain macromodels. In general, the phasedomain macromodel approach cannot be directly applied to the analysis of relaxation oscillators due to their strong nonlinear behavior. For relaxation oscillators detailed numerical simulations are thus unavoidable. In our simulations we also include the potential small mismatches among the series resistors. Fig. 18 shows the steady-state response of the array with parameters  $R_1^a = 41.6 \text{ k}\Omega$ ,  $R_2^a = 42.0 \text{ k}\Omega$ ,  $R_3^a = 42.4 \text{ k}\Omega$ , while  $R_1^b = R_2^b = R_3^b = 4 \text{ k}\Omega$  and for the transistor aspect

<sup>&</sup>lt;sup>2</sup>The two coupled oscillators are a dynamic system with four state variables: the external variables  $V_{s_1}(t)$ ,  $V_{s_2}(t)$  and the intrinsic variables  $V_{c_1}(t)$ ,  $V_{c_2}(t)$  of the VO<sub>2</sub> devices.

Fig. 16. Responses of oscillators with small mismatch  $R_{s_1} = 47 \,\mathrm{k}\Omega$  and  $R_{s_2} = 46.5 \,\mathrm{k}\Omega$ , and strong coupling  $R_c = 20 \,\mathrm{k}\Omega$ .

Fig. 17. Chain array with three coupled VO2 relaxation oscillators.

ratio W/L = 6. For such a coupling strength, the array responses achieve mutual frequency synchronization with the regular phase separation among the oscillators close to  $2\pi/3$ (phase misalignment is  $< 3^{\circ}$ ). This behavior definitely agrees with that found in [33], Fig. 7 case 4) in that reference, for an array of identical harmonic oscillators. However, simulations also show that for smaller coupling strengths, e.g. W/L = 2, the unmatched relaxation devices oscillate at slightly different frequencies (i.e., mutual synchronization is not reached) and thus relative phase differences vary in time. By contrast, when a too strong coupling strength is fixed, e.g. W/L = 10, the circuit in Fig. 17 ceases to oscillate and its response converges to a stationary equilibrium state. We conclude that for arrays of VO<sub>2</sub>-based relaxation oscillators, detailed simulations are key to properly design the circuit parameters that can provide multi-phase oscillations with controlled phase separations.

## VI. CONCLUSION AND FUTURE PERSPECTIVE

In this paper, an electrical equivalent model of two-terminal devices fabricated with Vanadium dioxide material has been presented. The proposed model can incorporate the experimentally characterized critical voltages, variable device resistances

Fig. 18. Response of the oscillator array.

and switching time of the device hysteretic response. Extensive simulations and analytical derivations based on the proposed model have been employed to explain the dynamics of VO<sub>2</sub>based relaxation oscillators and to develop a robust design methodology. First application examples have been illustrated that include realization of voltage-controlled oscillators and oscillator arrays with precise phase-separation control. Many other applications are envisaged for VO2 devices: Low power MIT based coupled oscillator dynamics can be used for image and pattern matching/recognition, template matching and visual saliency. Such applications usually require associative processing that involves finding the "degree of match" between two quantities (e.g. input and stored template) [35]. Associative processing algorithms implemented in the Boolean computing framework which processes information in a binary (1 or 0) format are computationally expensive; an oscillator based non-Boolean approach that harnesses their non-linear phase and frequency synchronization dynamics can provide an energy efficient hardware platform [34] for such applications. Further, low-power MIT based oscillators with tunable coupling can be potential candidates in associative memories [9].

#### REFERENCES

- [1] N. Shukla, et al., "Synchronized charge oscillations in correlated electron systems." *Nature, Scientific reports*, 4, 2014.

- [2] R. Marathe, B. Bahr, W. Wang, Z. Mahmood, L. Daniel, and D. Weinstein, "Resonant Body Transistors in IBMs 32 nm SOI CMOS Technology," *Journal of Microelectromechanical Systems*, vol. 23, no. 3, pp. 636-650, June 2014.

- [3] S. Kaka, M. R. Pufall, W. H. Rippard, T. J. Silva, S. E. Russek, and J. a Katine, "Mutual phase-locking of microwave spin torque nanooscillators.," *Nature*, vol. 437, no. 7057, pp. 389-392, Sep. 2005.

- [4] R. van de Beek, E. Klumperink, C. Vaucher, and B. Nauta, Low-jitter clock multiplication: a comparison between PLLs and DLLs, *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 49, no. 8, pp. 555-566, Aug. 2002.

- [5] K. Lee et al., "A single-chip 2.4-GHz direct-conversion CMOS receiver for wireless local loop using multiphase reduced frequency conversion technique", *IEEE J. Solid-State Circuits*, vol. 36, no. 5, pp. 800-809, May 2001.

- [6] H. C. Chang, X. Cao, U. K. Mishra, R. York, "Phase Noise in Coupled Oscillators: Theory and Experiment," *IEEE Tran. Microwawe Theory* and Techniques, vol. 45, no. 5, pp. 605-615, May 1997.

- [7] T. Roska, A. Horvath, A. Stubendek, F. Corinto, G. Csaba, W. Porod, T. Shibata, and G. Bourianoff, "An Associative Memory with oscillatory CNN arrays using spin torque oscillator cells and spin-wave interactions architecture and End-to-end Simulator," *13th International Workshop on Cellular Nanoscale Networks and Their Applications* (CNNA), 2012, pp. 13.

- [8] M. Mirchev, L. Basnarkov, F. Corinto, L. Kocarev, "Cooperative Phenomena in Networks of Oscillators With Non-Identical Interactions and Dynamics," *IEEE Trans. Circuits and Syst. I: Regular Papers*, vol. 61, no. 3, pp. 811-819, Mar. 2014.

- [9] S. P. Levitan, Y. Fang, D. H. Dash, T. Shibata, D. E. Nikonov, and G. I. Bourianoff, Non-Boolean associative architectures based on nano-oscillators, 13th International Workshop on Cellular Nanoscale Networks and Their Applications (CNNA), 2012, pp. 16.

- [10] F. C. Hoppensteadt and E. M. Izhikevich, Oscillatory neurocomputers with dynamic connectivity, Phys. Rev. Lett., vol. 82, pp. 2983-2986 (1999).

- [11] S. Datta, N. Shukla, M. Cotter, A. Parihar, A. Raychowdhury, "Neuro Inspired Computing with Coupled Relaxation Oscillators", *Design Automation Conference (DAC-2014)*, Jun. 2014, pp. 1-6.

- [12] P. Maffezzoni, B. Bahr, Z. Zhang, and L. Daniel, "Oscillator Array Models for Associative Memory and Pattern Recognition," *IEEE Trans. Circuits and Syst. I: Regular Papers*, vol. 62, no. 6, pp. 1591-1598, Jun. 2015.

- [13] A. Parihar, N. Shukla, S. Datta, A. Raychowdhury, "Synchronization of pairwise-coupled, identical, relaxation oscillators based on metalinsulator phase transition devices: A Model Study," *Journal of Applied Physics*, vol. 117, pp. 054902, Feb. 2015.

- [14] A. Zimmers, et al., "Role of Thermal Heating on the Voltage Induced Insulator-Metal Transition in VO2," *Phys. Rev. Lett.* 110, 056601, 2013.

- [15] T. S. Jordan, et al. "Model and Characterization of VO2 Thin-Film Switching Devices," *IEEE Trans. Electron Devices*, vol. 61, no. 3, pp. 813-819, Mar. 2014.

- [16] N. Sugimoto, S. Onoda, and N. Nagaosa, "Field-induced metalinsulator transition and switching phenomenon in correlated insulators," *Phys. Rev. B*, vol. 78, no. 15, p. 155104, Oct. 2008.

- [17] L. A. L. de Almeida, et al., "A hysteresis model for a vanadium dioxide transition-edge microbolometer," *IEEE Trans. on Instrumentation and Measurement*, vol. 50, no. 4, pp. 1030-1035, Aug. 2001.

- [18] A. Beaumont, J. Leroy, J.-C. Orlianges and A. Crunteanu, "Currentinduced electrical self-oscillations across out-of-plane threshold switches based on VO2 layers integrated in crossbars geometry," *Journal of Applied Physics*, vol. 115, pp. 154502, 2014.

- [19] H. T. Kim et al., "Electrical oscillations induced by the metal-insulator transition in VO2," *Journal of Applied Physics*, vol. 107, pp. 023702, 2010.

- [20] T. Driscoll et al., "Current oscillations in Vanadium Dioxide: evidence for electrically triggered percolation avalanches," *Physical Review B*, vol. 86, pp. 094203, Sept. 2012.

- [21] A. Kar, N. Shukla, E. Freeman, H. Paik, H. Liu, R. Engel-Herbert, S. S. N. Bhardwaja, D. G. Schlom, and S. Datta, "Intrinsic electronic switching time in ultrathin epitaxial vanadium dioxide thin film," *Applied Physics Letters*, vol. 102, no. 7, pp. 072106, 2013.

- [22] C. J. Hu, Self-sustained oscillation in an RH-C or RH-L circuit containing a hysteresis resistor RH, *IEEE Trans. Circuits Syst.*, vol. 33, no. 6, pp. 636-641, Jun. 1986.

- [23] M. P. Kennedy and L. O. Chua, "Hysteresis in electronic circuits: A circuit theorist's perspective," *Int. J. Circuit Theory & Applications*, vol. 19, no. 5, pp. 471-515, Sep. 1991.

- [24] P. Maffezzoni, L. Daniel, N. Shukla, S. Datta, A. Raychowdhury, V. Narayanan, "Modeling Hysteresis in Vanadium dioxide Oscillators," *IET Electronics Letters*, vol. 51, no. 11, pp. 819-820, Jun. 2015.

- [25] A. S. Elwakil, Low voltage relaxation oscillator, *Electronics Letters*, vol. 36, no. 15, pp. 1256-1257, Jul. 2000.

- [26] A. Elwakil, S. Ozoguz, "Explain Hysteresis in Electronic Circuits: Robust Simulation and Design Examples", *IEEE International Conference* on Electronics, Circuits and Systems (ICECS'06), pp. 244-247, 2006.

- [27] C. Verhoeven, "First order oscillators," *Ph.D. dissertation*, Delft University of Technology, 1990.

- [28] C. Verhoeven, J. Sneep, "A new low-noise 100MHz balanced relaxation oscillator," *IEEE Journal of Solid-state Circuits*, vol. 25, no. 3, pp. 692-698, Mar. 1990.

- [29] Virtuoso Spectre Circuir Simulator RF Analysis User Guide, Product Version 7.2, Cadence Design Syst., San Jose, CA, May 2010.

- [30] D. Harutyunyan, J. Rommes, J. ter Maten, W. Schilders, "Simulation of Mutually Coupled Oscillators Using Nonlinear Phase Macromodels

Applications," *IEEE Trans. on Computer-Aided-Design of Integrated Circuits and Systems*, vol. 28, no. 10, pp. 1456-1466, Oct. 2009.

- [31] P. Maffezzoni, "Synchronization Analysis of Two Weakly Coupled Oscillators Through a PPV Macromodel," *IEEE Trans. Circuits and Syst. I: Regular Papers*, vol. 57, no. 3, pp. 654-663, Mar. 2010.

- [32] M. Bonnin, F. Corinto, "Phase Noise and Noise Induced Frequency Shift in Stochastic Nonlinear Oscillators" *IEEE Trans. Circuits and Syst. I: Regular Papers*, vol. 60, no. 8, pp. 2104-2115, Aug. 2013.

- [33] P. Maffezzoni, B. Bahr, Z. Zhang, and L. Daniel, "Analysis and Design of Weakly Coupled Oscillator Arrays Based on Phase-Domain Macromodels," *IEEE Trans. Computer-Aided-Design of Integrated Circuits* and Systems, vol. 34, no. 1, pp. 77-85, Jan. 2015.

- [34] A. Parihar, N. Shukla, S. Datta, and A. Raychowdhury, "Exploiting Synchronization Properties of Correlated Electron Devices in a Non-Boolean Computing Fabric for Template Matching," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 4, no. 4, pp. 450-459, Oct. 2014.

- [35] N. Shukla, et al., "Pairwise Coupled Hybrid Vanadium Dioxide-MOSFET (HVFET) Oscillators for Non-Boolean Associative Computing," *IEEE International Electron Devices Meeting (IEDM)*, 2014, pp. 28.7.1-28.7.4.

**Paolo Maffezzoni** (M'08–SM'15) holds a MS degree in electronic engineering and a Ph.D. degree in electronic instrumentation. Since 2004, he has been an Associate Professor of electrical engineering at Politecnico di Milano, Italy, where he teaches basic Circuit Theory. His research interests include analysis, simulation and design of nonlinear dynamical circuits and systems. In the last years, he has contributed to develop a general methodology for modeling and simulation of systems of oscillating devices. The method has applications in the field

of analog and mixed-signal circuits, and in non-conventional computing. He has over 120 research publications among which 63 papers in international journals. He is currently serving as an Associate Editor for the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems and as a member of the Technical Program Committee of IEEE/ACM Design Automation Conference (DAC).

Luca Daniel (S'98-M'03) received the Ph.D. degree in Electrical Engineering from the University of California, Berkeley, in 2003. He is currently a Full Professor in the Electrical Engineering and Computer Science Department of the Massachusetts Institute of Technology (MIT). Industry experiences include HP Research Labs, Palo Alto (1998) and Cadence Berkeley Labs (2001). His current research interests include integral equation solvers, uncertainty quantification and parameterized model order reduction, applied to RF circuits, silicon photonics,

MEMs, Magnetic Resonance Imaging scanners, and the human cardiovascular system. Prof. Daniel was the recipient of the 1999 IEEE Trans. on Power Electronics best paper award; the 2003 best PhD thesis awards from the Electrical Engineering and the Applied Math departments at UC Berkeley; the 2003 ACM Outstanding Ph.D. Dissertation Award in Electronic Design Automation; the 2009 IBM Corporation Faculty Award; the 2010 IEEE Early Career Award in Electronic Design Automation; the 2014 IEEE Trans. On Computer Aided Design best paper award; and seven best paper awards in conferences.

Nikhil Shukla received the B.S. degree in electronics and telecommunications engineering from the University of Mumbai, Mumbai, India, in 2010. He is currently working toward the Ph.D. degree in electrical engineering in the Department of Electrical Engineering, The Pennsylvania State University, University Park, PA, USA.

Suman Datta (F13) received the B.S. degree in electrical engineering from the Indian Institute of Technology, Kanpur, India, in 1995, and the Ph.D. degree in electrical and computer engineering from the University of Cincinnati, Cincinnati, OH, USA, in 1999. From 1999 to 2007, he was a member of the Logic Technology Development Group, Intel Corporation. He was instrumental in the demonstration of III-V quantum-well transistors operating at room temperature with a record energy delay product, the first experimental demonstration of high-

performance high-k/metal gate CMOS transistors, and the invention and demonstration nonplanar trigate transistors. In 2007, he was the Joseph Monkowski Associate Professor of Electrical Engineering with Pennsylvania State University, University Park, PA, USA, where he is currently a Professor of Electrical Engineering. He is the holder of more than 160 U.S. patents. His group is exploring new materials and novel device architecture for CMOS enhancement and replacement for future energy-efficient computing applications. Dr. Datta is a Distinguished Lecturer of the IEEE Electron Devices Society.

Arijit Raychowdhury (M07–SM13) received the B.E. degree in electrical and telecommunication engineering from Jadavpur University, Kolkata, India, and the Ph.D. degree in electrical and computer engineering from Purdue University, West Lafayette, IN, USA. He is currently an Associate Professor in the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA, where he joined in January, 2013. His industry experience includes five years as a Staff Scientist in the Circuits Research Lab, Intel Corporation and

a year as an Analog Circuit Designer with Texas Instruments Inc. His research interests include digital and mixed-signal circuit design, design of on-chip sensors, memory, and device-circuit interactions. He holds more than 25 U.S. and international patents and has published over 100 articles in journals and refereed conferences. Dr. Raychowdhury is the winner of the Intel Labs Technical Contribution Award, 2011; Dimitris N. Chorafas Award for outstanding doctoral research, 2007; the Best Thesis Award, College of Engineering, Purdue University, 2007; Best Paper Awards at the International Symposium on Low Power Electronic Design (ISLPED) 2012, 2006; IEEE Nanotechnology Conference, 2003; SRC Technical Excellence Award, 2005; Intel Foundation Fellowship 2006, NASA INAC Fellowship 2004, and the Meissner Fellowship 2002.